# WASTE NOT, WANT NOT!

Managing Relational Data in Asymmetric Memories

# Waste Not, Want Not!

### Managing Relational Data in Asymmetric Memories

#### ACADEMISCH PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit van Amsterdam op gezag van de Rector Magnificus Prof. dr. D. van den Boom

ten overstaan van een door het College voor Promoties ingestelde commissie, in het openbaar te verdedigen in de Agnietenkapel op vrijdag 1 mei 2015, te 12:00 uur door Holger Pirk geboren te Potsdam, Duitsland

#### Promotiecommissie

Promotors: Prof. dr. M. L. Kersten

Prof. dr. S. Manegold

Overige leden: Prof. dr. J. Gehrke

Dr. G. Graefe

Prof. dr. P.M.A. Sloot Prof. dr. C.T.A.M. de Laat Prof. dr. J.A. Bergstra

#### **Faculteit**

Faculteit der Natuurwetenschapen, Wiskunde en Informatica Universiteit van Amsterdam

The research reported in this thesis has been partially carried out at *CWI*, the Dutch National Research Laboratory for Mathematics and Computer Science, within the theme *Database Architectures and Information Access*, a subdivision of the research cluster *Information Systems*.

The research reported in this thesis has been partially carried out as part of the continuous research and development of the MonetDB open-source database management system.

SIKS Dissertation Series No. 2015-18

The research reported in this thesis has been carried out under the auspices of SIKS, the Dutch Research School for Information and Knowledge Systems.

The work reported here has partly been funded by the EU-FP7-ICT project TELEIOS.

Published by: Uitgeverij BOXPress, s-Hertogenbosch

#### Abstract

Computer systems are not the monolithic machines they used to be. In the early days of computer science (until the late 70s), most computer systems included exactly one component to perform a given task: one (type of) disc for persistence, one CPU for processing and one volatile RAM to hold intermediate data. Today, the architecture has developed into a heterogeneous landscape of components: discs, SSDs, RAM, NVRAM, GPUs and CPUs with a hierarchy of caches – all working together to accomplish a given task. However, making efficient use of all of these devices is difficult: slow interconnects make communication and synchronization of these devices costly and motivate sophisticated co-operation strategies to minimize such communication. While developing an efficient cross-device co-operation strategy is far from trivial, there is a fundamental characteristic of computer hardware that can be exploited:

While memory component properties are asymmetric (fast&small vs. slow&large), so is data access (hot vs. cold, sequential vs random).

In this thesis, we study the management of relational data in modern, i.e., asymmetric computer systems. We explore different strategies to identify asymmetries in persistent data, map them to asymmetries in the memory landscape and, eventually, exploit them to increase query processing performance. To this end, we study memory conscious decomposition and storage of data at different granularities: relations, vertical partitions, single attributes as well as individual bits. In the interest of conciseness, we exclude techniques that require auxilliary data structures such as indices or horizontal partitioning which come with significant maintenance overhead.

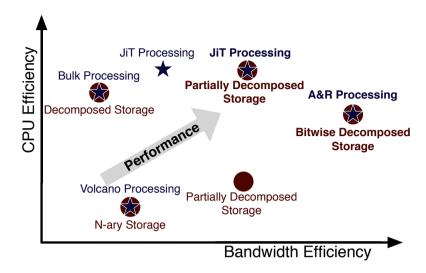

Further, we argue that, when managing memory-resident data, the problem of optimal data placement is tightly connected to the efficiency of the query processing paradigm and can, therefore, not be studied in isolation. Consequently, we also investigate the connection between storage model and processing paradigm. In the case of decomposition at partition granularity we identify Just-in-Time compilation as the only viable query processing model. In the case of distribution at the granularity of individual bits, we develop a novel processing paradigm that efficiently exploits the asymmetries in the underlying data and memory components.

#### Samenvatting

Computersystemen zijn niet de monolithische machines die ze vroeger waren. In het begin van de computerwetenschappen (tot het einde van de jaren '70) omvatten de meeste computersystemen precies n component voor elke taak: een soort disc voor het opslaan, een CPU voor het verwerken en een volatiel RAM voor het houden van intermediaire data. Tegenwoordig is de architectuur ontwikkeld tot een heterogeen landschap van componenten: discs, SSD's, RAM, NVRAM, GPU en CPU's met een hiërarchie van caches - die allemaal samenwerken om een bepaalde taak te volbrengen. Echter, efficiënt gebruik van al deze apparaten is moeilijk: trage interconnecties maken de communicatie en synchronisatie van deze apparaten duur en motiveren geavanceerde samenwerkingsstrategieën om de communicatie zoveel mogelijk te beperken. Terwijl het ontwikkelen van een efficiënt crossdevice samenwerkingsstrategie niet triviaal is, is er een fundamentele eigenschap van computer hardware die kan worden geëxploiteerd:

Eigenschappen van geheugencomponenten zijn asymmetrisch (snel&klein vs. langzaam&groot), en dat geldt ook voor de toegang tot de gegevens (warm vs. koud, opeenvolgend vs. random).

In dit proefschrift onderzoeken wij het beheer van relationele data in de moderne, dat wil zeggen, asymmetrische computersystemen. Wij onderzoeken verschillende strategieën om asymmetrieën in data management applicaties te identificeren, deze met asymmetrieën in de componenten van het geheugen te matchen en deze uiteindelijk te gebruiken om de prestaties te verbeteren. Hiervoor onderzoeken wij de memory conscious decompositie en opslag van gegevens op verschillende granulariteiten: relaties, (verticale) partities, attributen en individuele bits.

Verder voeren wij aan dat het probleem van een optimale plaatsing van gegevens strak is verbonden met het paradigma van queryverwerking en om die redden niet geïsoleerd kan worden onderzocht. Daarom hebben wij ook de samenhang onderzocht tussen het opslag-paradigma en het verwerking-paradigma. In het geval van decompositie op granulariteit van de partitie identificeren wij Just-in-Time compilatie als het enige rendabele query processing model. In het geval van een verdeling op de granulariteit van de individuele bits, ontwikkelen wij een nieuw verwerking-model dat efficiënt gebruik maakt van de asymmetrieën in de onderliggende gegevens en de componenten van het geheugen.

#### Acknowledgements

As is the case with many things, a thesis tells less about the matter at hand than about the person behind it. Consequently, acknowledgements should be more about the people that helped shape me as a person than about the people that contributed specifically to this thesis (though they still deserve mentioning).

For this reason I want to first mention my grandmother Christiane Pirk who taught me to always consider the human factor in things. My parents Heike and Thomas as well as my brother Norbert helped lay the groundwork for my learning about the scientifc approach to problems. I thank my supervisors Martin Kersten and Stefan Manegold for honing my skills and the insight that inspiration as well as rigor are the key ingredients to good science. Ulf Leser deserves mention for instructing me on the importance of style and clarity in argumentation (even though we sometimes disagree on the particular style). My family, Anja, Lara and Julina added a broader perspective to my work, if only by forcing me to explain it to them.

Naturally, the number of people that contributed to my thesis in thought and deed is beyond what is feasible to enumerate here. I will, however, do my best and appologize half-heartedly to those I failed to mention: thank you, Halldóra, Thibault, Jaldert, Yağiz, Eleni, Stratos, Florian, Peter, Sandor, Marcin, Erietta, Duc, Romulo, Eleftherios(os?), Kostis, Fabian, Sjoerd, Hannes, Jennie, Mrunal and Bart.

# Contents

|   | Intr | roduction                 |                    |  |

|---|------|---------------------------|--------------------|--|

|   | 1.1  | Hardware Conscious Data   | Management         |  |

|   | 1.2  |                           | e Memory Hierarchy |  |

|   | 1.3  | This Thesis               |                    |  |

|   |      | 1.3.1 Objective           |                    |  |

|   |      |                           | ered Publications  |  |

| 2 | Cor  | mputer System Architec    | ture               |  |

|   | 2.1  |                           | Principles         |  |

|   |      | 2.1.1 Machine Balance     |                    |  |

|   |      | 2.1.2 Data Access Local   | ity                |  |

|   |      | 2.1.3 The Memory Hiera    | archy              |  |

|   |      | 2.1.4 Latency Hiding .    |                    |  |

|   | 2.2  | Heterogeneity             |                    |  |

|   |      | 2.2.1 Monolithic System   | s                  |  |

|   |      | 2.2.2 Heterogeneous Sys   | tems               |  |

|   |      | 2.2.3 Programming Acce    | elerator Cards     |  |

| 3 | Rel  | ational Data Manageme     |                    |  |

|   | 3.1  | Relational Storage Models | 3                  |  |

|   |      |                           |                    |  |

|   |      | 3.1.2 (Fully) Decompose   | ed Storage         |  |

|   |      |                           | sed Storage        |  |

|   | 3.2  |                           | dels               |  |

|   |      | 3.2.1 Volcano-style Proc  | essing             |  |

|   |      | 3.2.2 Bulk Processing     |                    |  |

|   |      | 3.2.3 Query Compilation   | 1                  |  |

|   | 3.3  | Cost Models               |                    |  |

|   |      |                           | els                |  |

|   |      |                           | lels               |  |

CONTENTS 9

|   | 4.1 | Motivation                                          | . 39 |

|---|-----|-----------------------------------------------------|------|

|   | 4.2 | Partially Decomposed Storage in HyPer               | . 42 |

|   | 4.3 | Physical Schema Optimization                        | . 43 |

|   |     | 4.3.1 Storage Aware Cost Estimation                 | . 43 |

|   |     | 4.3.2 Extensions to the Generic Cost Model          | . 45 |

|   |     | 4.3.3 Modeling JiT Query Execution                  |      |

|   |     | 4.3.4 Cost-Driven Decomposition                     |      |

|   | 4.4 | Evaluation                                          |      |

|   |     | 4.4.1 Setup                                         |      |

|   |     | 4.4.2 The SAP-SD Benchmark                          |      |

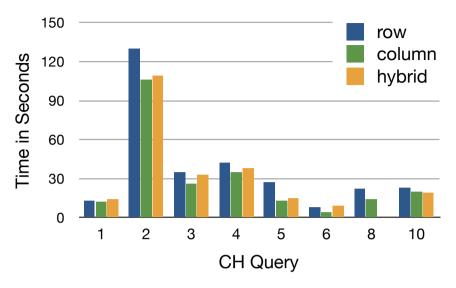

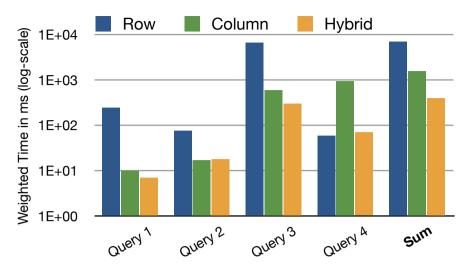

|   |     | 4.4.3 The CH-Benchmark                              | . 56 |

|   |     | 4.4.4 The CNET-Products Benchmark                   |      |

|   | 4.5 | Conclusion                                          |      |

| 5 | Exp | ploiting Asymmetries in Relational Operators        | 61   |

|   | 5.1 | Motivation                                          | 61   |

|   | 5.2 | Foreign Key Joins                                   |      |

|   | 5.3 | Setup                                               |      |

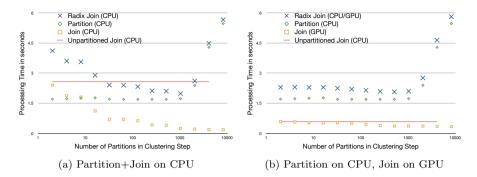

|   | 5.4 | Results                                             |      |

|   |     | 5.4.1 Applicability                                 |      |

|   | 5.5 | Conclusion                                          |      |

| 6 | Evr | ploiting Asymmetries in the Data                    | 71   |

| Ü | 6.1 | ~ ,                                                 |      |

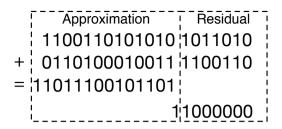

|   | 0.1 | 6.1.1 Decomposition                                 |      |

|   |     | 6.1.2 Distribution                                  |      |

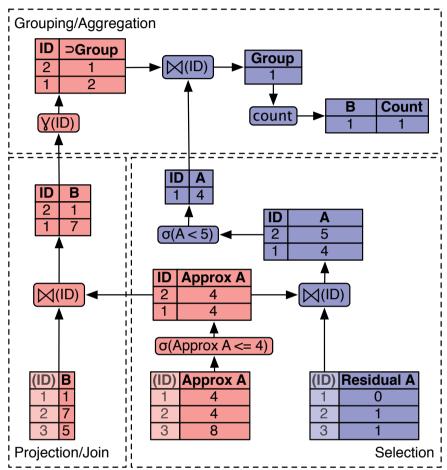

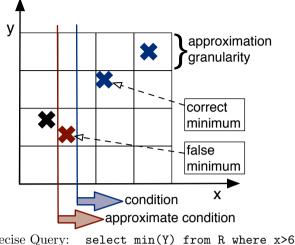

|   | 6.2 | Approximate & Refine Processing                     |      |

|   | 0.2 | 6.2.1 Phase 1: GPU Approximation                    |      |

|   |     | 6.2.2 Phase 2: CPU Refinement                       |      |

|   | 6.3 | The Prototype                                       |      |

|   | 0.0 | 6.3.1 Storage                                       |      |

|   |     | 6.3.2 Processing                                    |      |

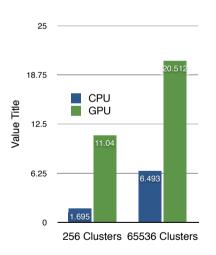

|   |     | 6.3.3 Evaluation                                    |      |

|   |     | 6.3.4 Query Processing                              |      |

|   | 6.4 | The Approximate & Refine Processing Model           |      |

|   | 0.4 | 6.4.1 Approximate & Refine Plans                    |      |

|   |     | 6.4.2 Approximation                                 |      |

|   |     | 6.4.3 The Translucent Join                          |      |

|   |     | 6.4.4 Approximate & Refine Operator Implementations |      |

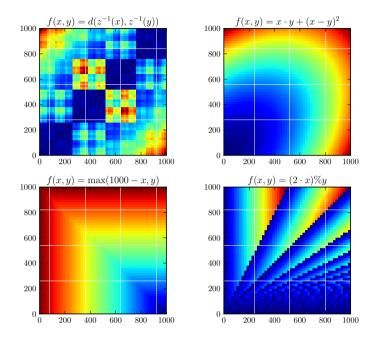

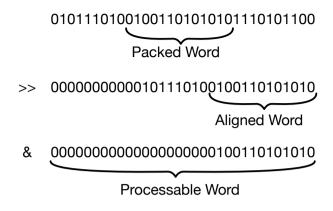

|   |     | 6.4.5 Arithmetics on Bitwise Decomposed Data        |      |

|   | 6.5 | 1                                                   |      |

|   | 6.5 | Managing Large Results                              |      |

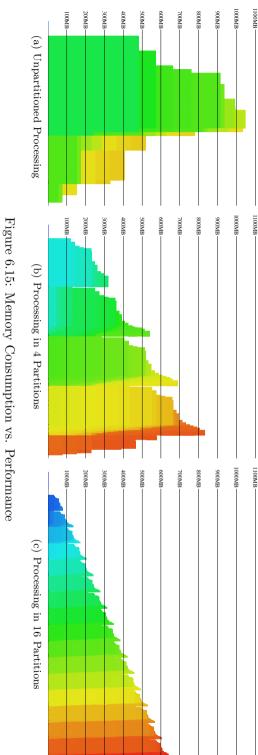

|   |     | 6.5.1 Partitioned Processing                        |      |

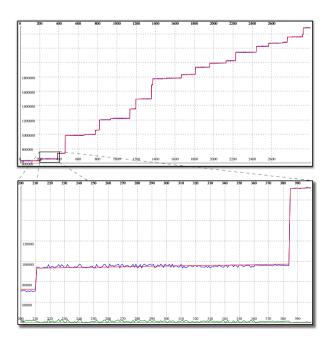

|   | 6.6 | 6.5.2 Result Compression                            |      |

|   | 6.6 | The System                                          |      |

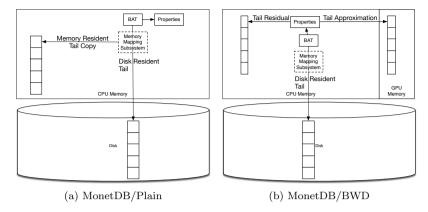

|   |     | 6.6.1 Decomposed Storage                            |      |

|   |     | 6.6.2 Schema Manipulation                           | 102  |

10 CONTENTS

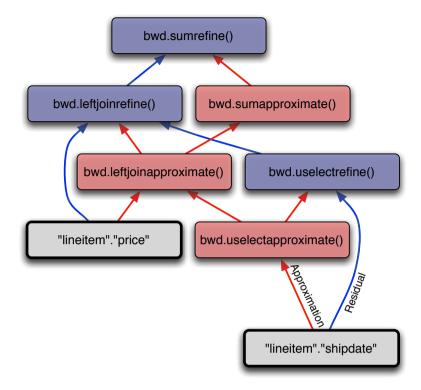

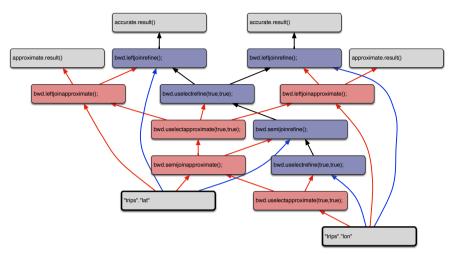

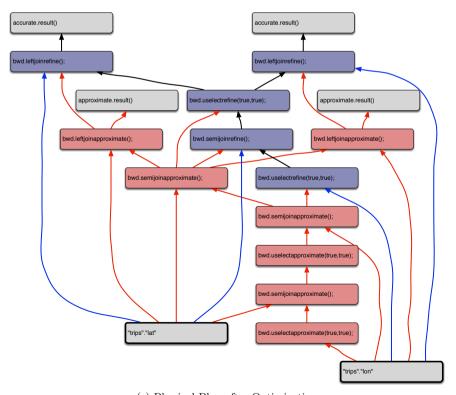

|    |        | 6.6.3 Plan Generation                           | 103         |

|----|--------|-------------------------------------------------|-------------|

|    |        | 6.6.4 (Rule-based) Query Optimization           | 104         |

|    |        |                                                 | 106         |

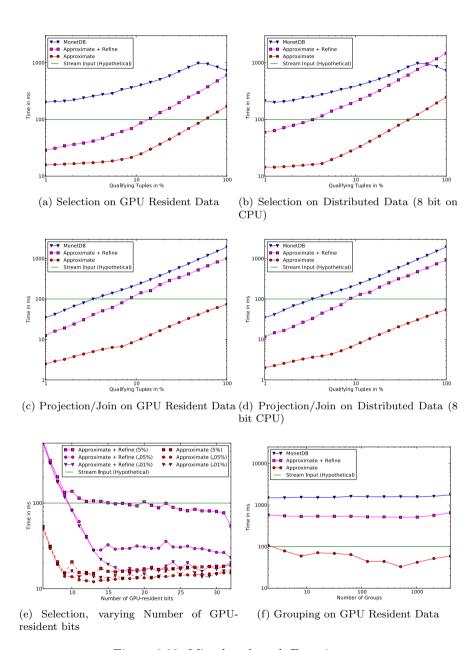

|    | 6.7    |                                                 | 108         |

|    |        |                                                 | 108         |

|    |        |                                                 | 108         |

|    |        |                                                 | 110         |

|    |        | 6.7.4 Appraisal                                 | 116         |

| 7  | Visi   | ion: A DBMS Designed for Heterogeneous Hardware | 117         |

|    | 7.1    |                                                 | 117         |

|    | 7.2    |                                                 | 119         |

|    | 7.3    | Assessing the Potential                         | 120         |

|    | 7.4    | Reactive Data Management                        | 123         |

|    |        | 7.4.1 Reactive Applications                     | 123         |

|    |        | 7.4.2 A Reactive DBMS Architecture              | 124         |

|    |        | 7.4.3 Prototype                                 | 125         |

|    | 7.5    | Related Work                                    | 127         |

|    |        | 7.5.1 Reactive Application Frameworks           | 127         |

|    |        | 7.5.2 Highly Parallel Data Management Systems   | 128         |

|    | 7.6    | Challenges                                      | 129         |

|    | 7.7    | Opportunities                                   | 130         |

|    | 7.8    | Conclusion                                      | 131         |

| 8  | The    | Big Picture                                     | 133         |

|    | 8.1    |                                                 | 133         |

|    |        | 8.1.1 Contributions in Data Placement           | 134         |

|    |        | 8.1.2 Contributions in Data Processing          | 135         |

|    | 8.2    |                                                 | 137         |

|    |        |                                                 | 137         |

|    |        |                                                 | 140         |

| _  | ъ      |                                                 | - 40        |

| 9  |        |                                                 | 149         |

|    | 9.1    | 0                                               | 149         |

|    |        | * *                                             | 149         |

|    |        | 9                                               | 150         |

|    | 9.2    | 9                                               | 151         |

|    |        | 9                                               | 151         |

|    |        | 9.2.2 Opportunities                             | 151         |

| Bi | ibliog | graphy                                          | <b>15</b> 5 |

| Li | st of  | Figures                                         | 167         |

| Li | st of  | Tables                                          | 169         |

|    |        |                                                 | 171         |

|    |        |                                                 |             |

# Chapter 1

# Introduction

If you ask me what I want to achieve, it's to create an awareness, which is already the beginning of teaching.

Elie Wiesel

# 1.1 Hardware Conscious Data Management

Data Management, i.e., the storage, manipulation and querying of large amounts of data, used to be an exclusive problem of large companies like banks, insurances or energy companies. These companies had the resources to buy and maintain large computing machines that were customized for their needs and usually bundled with optimized software. Consequently, the Database Management System (DBMS) designs and implementations that originate from this age implement an architecture that works best if the software runs on the monolithic computing machines that were common during this age. In its extreme this paradigm culminated in the conception of Database Machines [1]: computer systems designed and optimized for the single purpose of running a DBMS - no operating system, no user interface. Some database machines even included specialized components such as diskheads with integrated logic. While highly efficient in terms of energy and processing performance, these machines tended to be very uneconomic: because of overspecialization, they could not be sold, and thus manufactured, at quantities needed for efficient production [2].

#### Database Machines were a flop.

The opposite concept has become known as *Commodity Hardware*: hardware (components) generic enough to run almost any conceivable application at moderate efficiency. The applications range from data management to text processing to physical simulations and even computer games. The economy of scale allows the very (cost-)efficient production and maintenance of such hardware [3], giving it a significant edge over more specialized systems. Unfortunately it prevents manufacturers from optimizing the hardware for

the intended application which results in less efficient operations. While suboptimal, the reduced efficiency is accepted and worked around to reap the benefits in maintainability and cost [4]: large scale web companies like Google, Facebook or LinkedIn almost exclusively use commodity hardware components for their infrastructure.

Commodity Hardware is a huge success.

To make commodity hardware as efficient as possible for as many applications as possible, hardware vendors try to identify and exploit common patterns in application behavior. One of these patterns is the distinction of data into hot and cold which can be exploited using hierarchical memory.

### 1.2 Data Temperature and the Memory Hierarchy

The notion of data temperature is quite intuitive as well as immensely useful: in essence it expresses the insight that some data items are accessed (i.e., read or written) more often than others. In the presence of hot and cold data, a system can be tuned such that accesses to "hot" data are accelerated at the expense of accesses to "cold" data.

One way of achieving this is by introducing hierarchical memory layers: instead of spending the available resources (money, transistors or energy) uniformly on a single layer of moderately fast memory, the system is designed to incorporate fast (usually small) layers and slower (usually larger) layers. The faster layers can, then, be used to store hot data in the hope that the benefits from faster accesses to hot data outweighs the additional costs for accessing cold data. Since the size of the fastest memory is usually smaller than the entire dataset, the presence of a memory hierarchy, naturally, raises the question of data placement. A simple rule of thumb for data placement was formulated [5] and frequently reassessed [6, 7]: the "five minute rule". This rule says that, if data is accessed less than once every x (five in the first version) minutes, it is considered cold and can be flushed to disk - otherwise it should be kept in memory. As we will show in this thesis, data placement has, in turn, a tremendous impact on the optimal way of processing the stored data.

#### 1.3 This Thesis

#### 1.3.1 Objective

Given the importance of data placement, the primary objective of this thesis is to answer the following question:

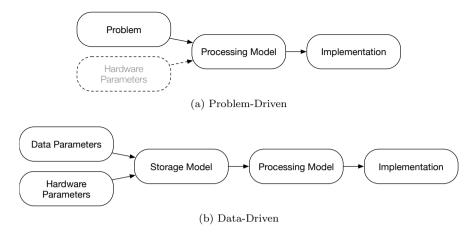

How should data be stored in the available layers of the memory hierarchy to make the best use of the available resources? As indicated above, we believe that the problem of selecting the optimal storage and processing model are intertwined and can, therefore, not be debated in isolation. To address these problems holistically, we identify and, when necessary, develop the appropriate processing model for each considered storage model.

13

#### 1.3.2 Structure and Covered Publications

This thesis studies problems at the intersection of data management and computer hardware research. While we assume basic knowledge in both of these domains, we provide the necessary background in two separate background chapters: in Chapter 2, we establish common ground knowledge about modern processors, hierarchical memory as well as modern instances of the concepts. In Chapter 3, we provide the same for data management system storage and processing models as well as the hardware-conscious prediction of data management performance. The reader may skip one, or even both of these chapters, at his or her discretion.

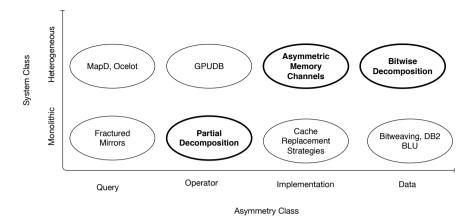

Since overall theme of this work is the exploitation of data access asymmetries and how they can be mapped to asymmetries of memory components, we dedicate each chapter to a class of asymmetry that we identified in data management applications.

In Chapter 4, we study asymmetries in the workload, i.e., queries that access only subsets of the attributes of tuples. This chapter is based on the following paper:

# • CPU And Cache Efficient Management Of Memory-Resident Databases

H. Pirk, F. Funke, M. Grund, T. Neumann, U. Leser, S. Manegold, A. Kemper, M. L. Kersten

IEEE International Conference on Data Engineering (ICDE) 2013

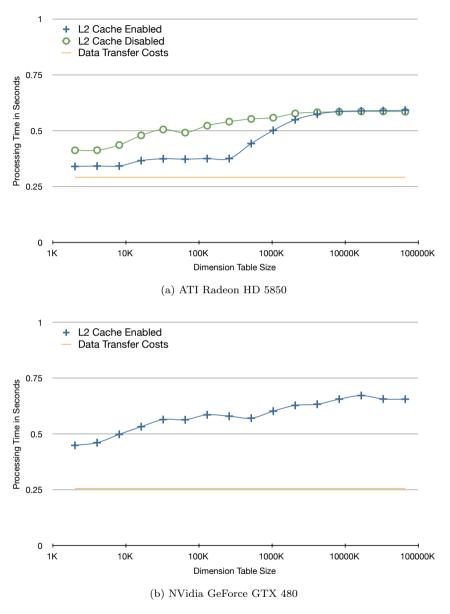

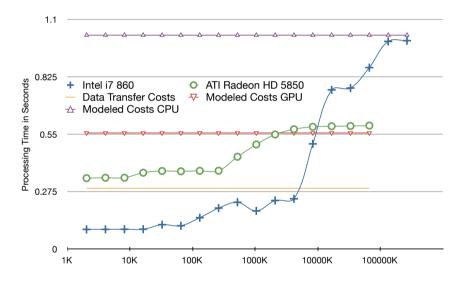

In Chapter 5, we concern ourselves with asymmetries found in relational operators. In particular we study the benefits of using asymmetric memory channels to speed up the performance of a very common operation in relational DBMSs: the positional join (a.k.a., Invisible Join or Indexed Foreign Key Join). This is based on the paper:

#### • Accelerating Foreign-Key Joins Using Asymmetric Memory Channels

H. Pirk, S. Manegold, M. L. Kersten

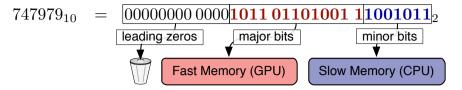

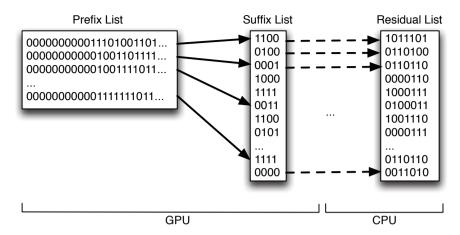

VLDB - Workshop on Accelerating Data Management Systems Using Modern Processor and Storage Architectures (ADMS) 2011 In Chapter 6, we aim at identifying asymmetries in the data itself that can be mapped to asymmetric memories irrespective of the workload of the system. In particular we study asymmetries in the significance of individual bits of data values. This chapter is based on a series of papers:

- X-Device Query Processing By Bitwise Distribution H. Pirk, T. H. J. Sellam, S. Manegold, M. L. Kersten International Workshop on Data Management on New Hardware (Da-MoN) 2012

- Waste Not... Efficient Co-Processing Of Relational Data H. Pirk, S. Manegold, M. L. Kersten IEEE International Conference on Data Engineering (ICDE) 2014

- ...Want Not Efficient Co-Processing of Relational Θ-joins H. Pirk, S. Manegold, M. L. Kersten Manuscript In Preparation

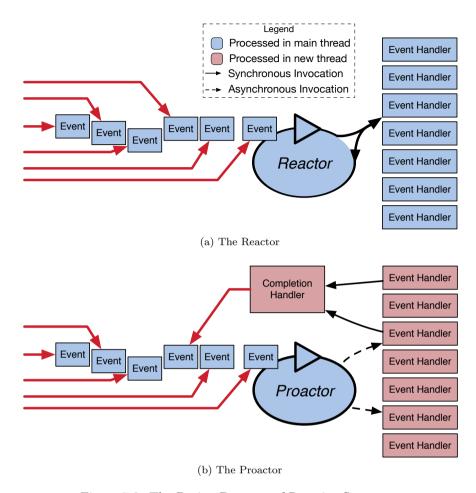

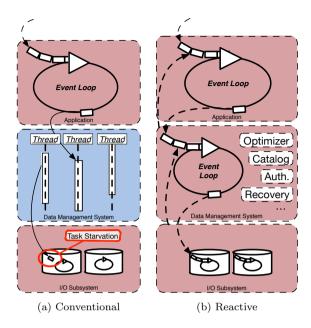

Chapter 7 is dedicated entirely to processing. However, we do not restrict ourselves to the query evaluation paradigm but broaden our focus to the entire DBMS architecture. In that, we address a problem that arose frequently in earlier chapters of this work: asynchronicity of hardware components in modern computer systems. To resolve this problem, we present a vision of a fundamentally different DBMS architecture based on the well-known Reactor Pattern. The chapter is based on the paper:

• The Missing Link - A call for a Reactive Data Management System Architecture

H. Pirk

Submitted to the International Conference on Extending Database Technology (EDBT) 2015

In Chapters 8, and 9, we put the contributions of this thesis in context: In Chapter 8, we summarize our contributions and provide a glimpse at the bigger picture. We also give an overview of work addressing similar or adjacent problems. Chapter 9 is dedicated to a discussion of problems that were left unaddressed in this thesis and research areas opened by our contributions.

# Chapter 2

# Computer System Architecture

As in all systems, economics is the key part of the objective function that determine[s] design.

Gordon Bell [8]

Computer system design is a complex and delicate process, in many respects more an art than a science. Like many arts, it is guided by experience and intuition rather than rigorous scientific investigation. Several pioneers of computer system design tried to capture their intuition in "Rules of Thumb" [8, 9] which, by means of textbooks [10], became design principles. Since the decisions that are based on these principles strongly influence the optimal implementation of a given piece of software, it is beneficial to be familiar with these principles. The intent of this chapter is to establish this familiarity as much as needed to follow the rest of this thesis.

# 2.1 Computer System Design Principles

Since many computer system design principles are based on patterns that are commonly found in computer software, we use this section to introduce the design principles (such as hierarchical memory) as well as the observations they are based on (such as the data access locality).

#### 2.1.1 Machine Balance

Since computer system design is driven by market requirements, the objective is to design a machine that creates maximum value given a certain budget. The value is usually measured in operations per time while the budget can be defined by various metrics such as price, energy consumption or heat dissipation. Since virtually every component stresses said budget, it is imperative to design a *balanced* system. There exist a variety of definitions for the term balanced [11, 12] that ultimately capture the same idea: all available components should reach the limit of their operational capacity at the level of system load. To encourage the development of balanced systems, Gene Amdahl formulated a rule of thumb:

A balanced computer system needs 1 MB of main memory capacity and 1Mbit per second of I/O bandwidth per MIPS of CPU performance.

While the formulation suggests eternal and universal validity, there are numerous flaws in such an overly general statement. Firstly, it is assumed that only three factors (CPU performance, memory capacity and disk bandwidth) determine the performance of the overall system. Secondly, this rule implies that the balance of the components can be determined irrespective of the purpose of the system, i.e., the application it will run when in use. Indeed, research has shown that most systems are unbalanced for most applications for I/O intensive workloads [12].

Whatever the shortcomings of this particular guideline, its mere existence signifies the importance of balance in computer systems.

#### 2.1.2 Data Access Locality

Since monolithic systems provide no architectural degrees of freedom at runtime, design decisions have to be based on static assumptions about the software to be run. An assumption that proved almost universally true is known as *Data Access Locality*: the expectation is that past accesses to data items provide hints towards future accesses. In particular, an access to a data item is expected to indicate either a) a (near-)future access to the same data item (known as *Temporal Locality*) or b) a (near-)future access to a data item in close proximity to the current one (known as *Spatial Locality*).

The assumption of *Data Access Locality* forms the basis for almost all performance enhancing techniques in the data access subsystem, the most important of which is hierarchical memory.

### 2.1.3 The Memory Hierarchy

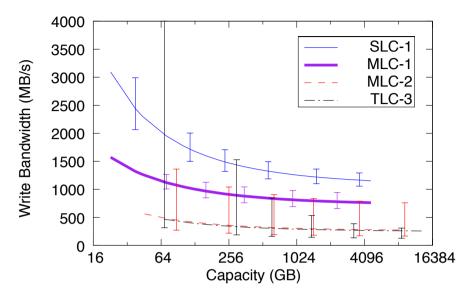

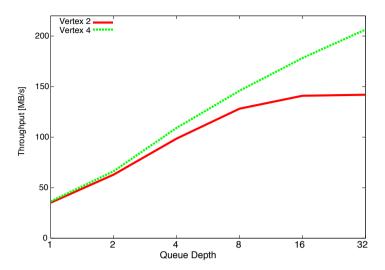

Any kind of memory component faces a fundamental trade-off between capacity and speed. This trade-off is mainly economic (larger, faster memory is simply more expensive to build) but also partially systemic since more memory is inherently harder to address: Resolving an integer address to a physical location on a chip or disk involves a decoding effort proportional to the length of the address [10]. Figure 2.1 shows that even devices of the same type (in this case flash memory) face a systemic conflict between storage capacity and performance<sup>1</sup> [13]. To resolve this conflict, most systems combine multiple devices into a memory hierarchy that speeds up localized access. Multiple levels of caches and Translation Lookaside Buffers (TLBs) speed up repetitive accesses to data items (or data items located on the same cache line or TLB-Block). Unfortunately, this even intensifies the existing trade-off because data items do not only have to be addressed, but

<sup>&</sup>lt;sup>1</sup>In Big Data terms: there is a conflict between data Volume and Velocity

located in the

Figure 2.1: Flash Memory<sup>1</sup> Capacity/Bandwidth [13] (layout adjusted)

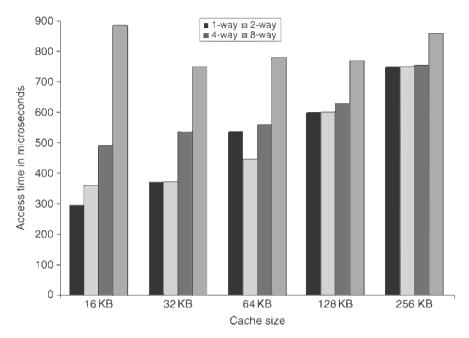

set of eligible slots. For that reason, the number of eligible slots for a given memory address is usually limited to a few. This parameter, *cache associativity*, has a significant impact on the cache's performance (see Figure 2.2): the lower it is, the lower the access time but also the higher the chance for harmful cache line evictions due to conflicts.

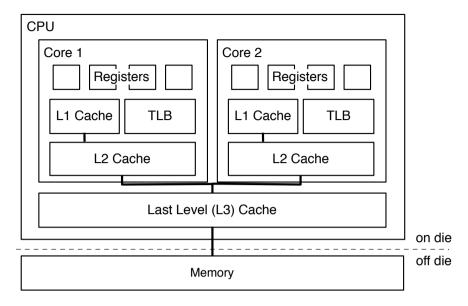

This fundamental trade-off between access time and capacity can be alleviated by combining different memory components with different parameters. Combining many such components leads to the infamous deep memory hierarchies (see Figure 2.3) with hard-to-predict runtime characteristics.

#### The Hierarchy - A Network

While it is convenient to think of the memory subsystems of a computer as hierarchical layers, this view obfuscates reality: even within a single CPU, there are sometimes multiple memory components at the same conceptual layer. Many modern CPUs, e.g., contain multiple Address translation caches (TLBs) with different characteristics such as size and even page size: common are "normal" (4 KB) and "huge" (2 MB) pages.

|   | Acronym | Explanation                                                          |

|---|---------|----------------------------------------------------------------------|

|   | SLC     | Single Level Cell, each two-state flash cell holds a single data bit |

| 1 | MLC-1   | Multi Level Cell, each four-state flash cell holds a single data bit |

|   | MLC-2   | Multi Level Cell, each four-state flash cell holds two data bits     |

|   | TLC     | Triple Level Cell, each eight-state flash cell holds three data bits |

Figure 2.2: Cache Access Time/Capacity Trade-off [10]

This network-like structure becomes even more apparent when considering computer systems that contain a central CPU as well as co-processing extension cards like General Purpose Graphics Processing Units (GPGPUs) or accelerators. These usually have internal memories as well as local caches transforming the memory hierarchy into a complex network of memory components. However, for convenience as well as consistence with earlier work, we will sometimes treat and denominate parts of the network as a hierarchy. As long as higher layers have access to data that is stored in lower layers, they form a hierarchy and can be treated as such.

#### Hardware vs. Software Controlled Memory

Next to latency, capacity and bandwidth, we characterize memory components by another trait: the locus of control. By our understanding, *Hardware Managed Memory* is any kind of memory component that has autonomy about its operations. This autonomy includes the liberty to reorganize and even delete (evict) stored data. Hardware Managed Memory can, therefore, not be used to (safely) store data, which limits its application to holding intermediate data items or copies of data items that are already persistent in other, usually slower, layers of the memory hierarchy. The most common instance of Hardware Managed Memory is the (associative) CPU cache <sup>2</sup>.

<sup>&</sup>lt;sup>2</sup>Another instance is Associative Memory

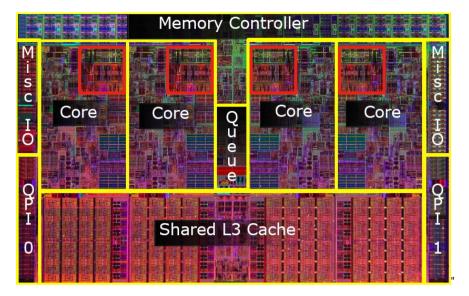

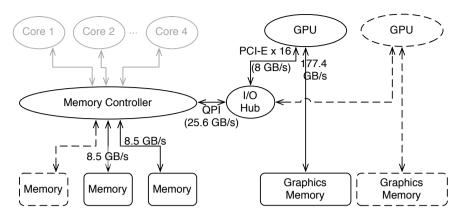

Figure 2.3: Intel Nehalem Memory Structure

Software Managed Memory is memory that is explicitly accessed using integer addresses. While the memory is at liberty to reorganize its internal storage (e.g., for wear-leveling in SSDs), it has to ensure that data that is written to an address can be retrieved from this address later on. Since the memory's management in software usually involves significant overhead, software managed memories are usually the ones at the lower end of the hierarchy. There are however, software managed low-latency caches like scratch pad memories or the local memory of a GPGPU's compute units.

### 2.1.4 Latency Hiding

Whenever two hardware components inter-operate, they send requests to one another. These requests can usually not be serviced right away, but involve a latency. Without additional measures taken, the requesting component would wait for the busy component even though it might have resources available to perform further work. To mitigate this effect, a number of techniques for *Latency Hiding* can be employed.

#### **Pipelining**

While not strictly speaking a latency hiding technique, CPU pipelining is the basis for many other optimizations. The idea is to break the execution of CPU instruction words into different stages like instruction fetching, decoding, register allocation, operand loading, execution, etc.. These stages

Figure 2.4: A CPU (Intel i7) Die [14]

can, then, be serviced by individual units. The units can be optimized in isolation or even replicated if they prove to be a bottleneck.

#### Out-of-Order Execution

A very common technique to hide component latency is based on the detection of independent work at runtime. If independent instructions are detected they can be evaluated in an order that suits the processor or even in parallel. The fetch and decode stages of an instruction, e.g., can be evaluated while the operands of the previous instruction are loaded into registers. This can effectively hide the latency of the caches or memory to supply an operand. Unfortunately, this does not come for free: the CPU first has to identify independent instructions. While control dependent instructions (conditional execution) are comparatively easy to identify, data dependent instructions (the outcome of instruction depending on the outcome of another) are hard. Complex reordering units are responsible to detect and exploit independent instructions for latency hiding.

#### Speculative Execution

Unfortunately, many applications are dominated by dependent instructions which are not eligible for out-of-order execution. To hide latencies in such applications, the CPU can resort to speculation: in many cases the outcome of, e.g., a condition evaluation can be anticipated based on historical behavior like previous evaluations of the same condition. Speculative execution is one of the most important performance improving techniques in

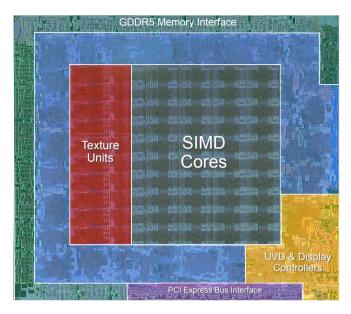

Figure 2.5: A GPU (ATI Radeon HD 4870) Die [15]

modern CPUs because without it any dependency in the instruction stream would cause stalling. From an instruction pipeline throughput perspective, this stalling (doing nothing) is as expensive as wrong speculation (doing the wrong thing). Thus, since there is no penalty for speculation, CPUs virtually never stall if there is potential for speculation.

#### (Cache Line) Prefetching

While technically an instance of speculative execution, cache line prefetching deserves special mention because it addresses a different case that adheres to different rules and, therefore, calls for different strategies.

While transferring and processing a fetched cache line in the CPU, the next accessed cache line is anticipated by a *Prefetching Unit*. If the confidence is high enough, a fetch instruction is issued to the memory system and the cache line is loaded into a slot of the Last Level Cache (LLC). A correctly prefetched cache line may hide memory access latency behind the time spent processing the data whilst incorrect prefetching a) causes unnecessary traffic on the memory bus and b) may evict a cache line that should have stayed cache-resident. Due to these potentially harmful effects, prefetching units generally follow a cautious strategy when issuing prefetch instructions.

**Prefetching strategies** vary among CPUs and are often complex and defensive up to not issuing any prefetch instructions at all. In our model, we assume an *Adjacent Cache Line Prefetching with Stride Detection* strategy

that is, e.g., implemented in the Intel Core Microarchitecture [16]. Using this strategy, a cache line is prefetched whenever the prefetcher anticipates a constant stride, i.e., a number of sequential accesses with a fixed number address increment. Although this seems a naïve strategy, its simplicity and determinism make it attractive for implementation as well as modeling. More complex strategies exist, but usually rely on the (partial) data access history of the executed program. These are generally geared towards more complex operations (e.g., high dimensional data processing or interleaved access patterns) yet behave similar to the Adjacent Cache Line Prefetcher in simpler cases like relational query processing.

#### Massive Parallelism

Recently, a fundamentally different paradigm for latency hiding has been adopted: massive parallelism. This paradigm follows the conviction that the best way to generate enough independent work is to force the software developer to implement his program in the form of many independent units of work (often called work items). This reduces latency hiding to merely suspending an execution thread and picking up another on a resource stall. This eliminates the need for instruction reordering or speculation and frees up on-die resources that can be used for other purposes such as more computational capacity or memory bandwidth. This enables massively parallel extension cards like (GP)GPUs or dedicated accelerators to provide computation power that is superior to that of conventional, i.e., speculating CPUs. To illustrate this, consider Figures 2.4 and 2.5: while the former depicts the die of a common CPU with functional units highlighted (Execution Units in red), the latter highlights the functional units of a GPU. The different paradigms become apparent in the number of transistors dedicated to execution: while the CPU hardly uses ten percent of estate for execution units, the GPU dedicates more than a third of the transistors to the (simplistic) executing cores. This is even more striking when considering the amount of estate spent on graphics-specific functionality like texturing and display controlling.

Unfortunately, the benefits of massively parallelism come at the costs of a significantly more involved programming model. Indeed, we believe that the complexity of the programming model merits an in-depth explanation that we provide later in this chapter (Section 2.2.3). Before that, however, we want to discuss the advantages and disadvantages of another aspect of modern hardware that will play an important role in the rest of this thesis: heterogeneity.

# 2.2 Heterogeneity

Heterogeneity refers, somewhat counter-intuitively, less to the diversity of employed hardware components themselves but to diversity of the computer systems that can be assembled from them.

#### 2.2.1 Monolithic Systems

While "heterogeneous system" has become a standard term in recent years, its opposite does not have such a convenient handle. Since we feel that the most important trait of heterogeneous systems is their extensibility, we will call their opposite "monolithic".

As implied by their name, monolithic computer systems are complex, integrated machines. The design goal is a machine that is composed of a fixed set of components, linked by a static network of fast interconnects. While the static, integrated nature of the network enables low latencies and high bandwidths, the challenge is to develop a system that is flexible enough to achieve balance for all applications that could be encountered.

To achieve this, hardware designers can draw from the previously introduced arsenal of techniques to balance their monolithic systems for many common applications. However, the goal of perfect, application-independent balance of monolithic systems remains utopian. Fortunately, given enough expertise and knowledge about the application, a system can be configured towards a certain application. The means of configuration are system extensions like disks, SSDs or accelerator cards. However, the application of such extensions effectively turns the system into a heterogeneous system.

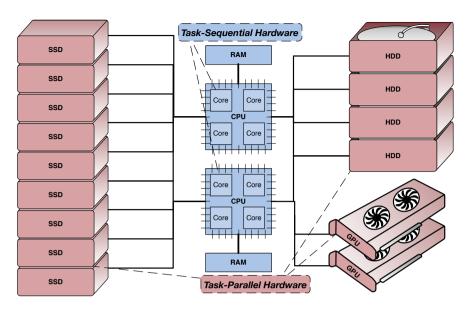

#### 2.2.2 Heterogeneous Systems

Heterogeneity is, at the same time, a blessing and a curse: it allows the creation of an application-specific, balanced system but it also creates significant problems other than the mere selection of applied components. The root of most of these problems lies in the loose links between the connected devices and the replication of components.

#### Interconnects

Exchanging data between the main memory and a device is the fundamental operation of any system I/O. To get a general impression of the integration of a GPGPU device into the host system's memory structure, consider Figure 2.6. A typical Intel® Nehalem-class test system is equipped with two memory channels (high end systems may have three) that are connected to the memory controller [17]. The specific bandwidth of these depends on the external clock frequency of the CPU but is in the range of 8 to 10 GB/s. The Memory Controller is connected to the I/O Hub through the QPI-bus which has a peak bandwidth of 25.6 GB/s [18]. In practice it may be used for other purposes like, e.g., cache-coherency among CPUs as well, which may put additional load on the bus. The I/O Hub controls the PCI-E bus and may, in theory, transfer up to 8 GB/s (16 PCI-E transfer lanes with 500 MB/s each) to each GPU device, currently up to a limit of 18 GB/s (the Intel X58 IOH supports up to 36 PCI-E lanes).

Figure 2.6: Architecture of a typical CPU/GPU System (dotted components are optional)

The data access granularity between the I/O Hub and the Memory is determined by the cache line size of the LLC<sup>3</sup> which is generally 64 bytes. The granularity on the PCI-bus is generally 64 bit but incurs a large overhead per word. The PCI controller, therefore, has the option of *PCI posting*: combining several PCI adjacent (write) requests into a single burst [21]. The maximum length of these bursts is implementation specific. In practice, random access to the host memory from the GPU should be avoided at all costs and is often unsupported by the hardware.

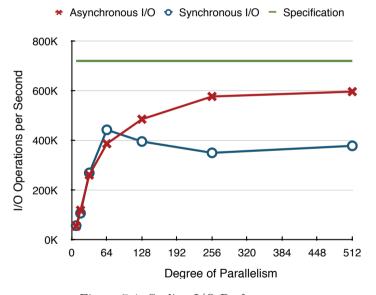

The transfer of data between the device and the CPU can be performed in one of two ways: controlled by the hardware, i.e., the DMA controller, or controlled by software running on the CPU itself (Memory Mapping). Depending on the need for preprocessing (e.g. pre-selection), either may have advantages. Unfortunately, some vendors only support a subset of the available techniques<sup>4</sup>. Since the host to device transfer is the limiting factor for data intensive applications (see Sections 5.2 and 5.4), however, it is crucial that both methods are implemented. We discuss the technical implementation of the transfer methods and their respective advantages in the following.

#### Memory Mapping of PCI Devices

The ability to map device memory into the addressable memory of a user process is an integral part of the x86 architecture<sup>5</sup>[17]. Historically, the

$<sup>^3\</sup>mathrm{more}$  accurately the burst size of the memory component [19, 20] which is usually co-designed with the LLC

$<sup>^4</sup>$ E.g., the ATI Stream SDK 2.4 supports neither Memory Mapping nor non-Bulk (Device-initiated) DMA on Linux

<sup>&</sup>lt;sup>5</sup>and most other platforms as well

Northbridge took care of all memory accesses on the "fast" connections, i.e., RAM, AGP and PCI-E devices.

Most current CPUs come with an integrated memory controller and only rely on the Northbridge for real I/O. This architecture will be our focus. When accessing a memory address that falls into the designated area for memory mapped devices, the CPU sends it to the *Northbridge (a.k.a. I/O Hub)* using QPI (or the AMD equivalent: HyperTransport). For PCI-E devices, the Northbridge takes care of wrapping the memory access into the appropriate Bus protocol and sending it to the device. PCI posting gives Memory Mapped Devices similar access characteristics as regular memory: data is accessed in blocks that are similar to cache lines for regular memory.

#### Direct Memory Access (DMA)

DMA gives a device access to the system's main memory without involving the CPU and its internal buses for every single transfer. DMA is controlled by the device and can be initiated by the CPU or the device. In the earlier case, which is more interesting to us, the CPU prepares an area of the memory for DMA (this is sometimes called *pinning* of memory) and triggers the transfer by signaling the device. In the case of PCI, the device becomes the Bus-Master, requests (parts of) the prepared region and issues an interrupt to the CPU once it is done [22]. Pinning the memory can be an expensive operation. Depending on the support by the hard- and software it might involve copying the data to a contiguous area in (kernel-)memory. Some current PCI-E devices support scatter/gather-lists that avoid this additional copy. Regardless of the necessity for this copy, the Operating System has to ensure consistency of the transferred data by flushing the caches and preventing the paging to disk. Setting up a DMA transfer is, thus, costly and should be done only for large (several megabytes at least) amounts of data.

If data resides readily in main memory, we expect DMA to perform better than Memory Mapping because it avoids an additional pass through the CPU's memory hierarchy. If, however, the data has to be modified (e.g., preselected or partitioned) it has to pass through the CPU in any case. In this case we expect Memory Mapping to outperform DMA because it avoids materializing the intermediates in RAM. Unfortunately, the implementation of host to device transfer, especially on "exotic" platforms (i.e., not Windows) is often not optimally exploiting the available hardware features, thus limiting the actual performance.

### 2.2.3 Programming Accelerator Cards

Most extension cards are designed as accelerators to existing systems, providing resources that the host-systems lacks: massive computation power and bandwidth. Since easy programmability, generality or the support of legacy software is not one of the design goals, the programming of these

cards is significantly different from "conventional" CPU programming. We will provide an overview of the peculiarities of accelerator card programming in this section. While most of the presented concepts apply to other cards of accelerators, we will focus on the programming of GPGPUs using OpenCL.

#### **Device Memory**

The internal RAM (VRAM) of a GPU has a bandwidth in the range of triple-digit GB/s but also a comparatively high latency of around 200 to 300 cycles as opposed to common CPU memory latency of 50 to 60 cycles. This conscious design decision is mitigated by the high degree of parallelism: When used correctly, the computation of one thread can hide the memory access latency of another. Correctly exploiting this parallelism is, however, not trivial. To simplify the programming of massively parallel computation devices, vendors rely on the kernel programming model. While supporting massive parallelism, this model comes with a number of limitations and pitfalls.

#### Massively Parallel Programming

Programming the high number of cores of a GPU in an imperative language with explicit multithreading is a challenging task. To simplify GPU programming, a number of competing technologies based on the kernel programming model have been introduced. The most prominent ones are: DirectCompute, CUDA [23] and OpenCL [24]. Whilst the earlier two are proprietary technologies, the later is an open standard that is supported by many hardware vendors on all major software platforms. The supported hardware does not just include GPUs, but CPUs as well: Intel and AMD provide implementations for their CPUs, AMD and NVidia for GPUs. Apple, one of the driving forces behind OpenCL, ships their current OS version with an OpenCL implementation for both GPUs and CPUs. The portability does, however, come at a price: to support a variety of devices, OpenCL has to abstract away any device specific capabilities and resort to the least common denominator. This radically limits the programming model. In addition, the performance characteristics of the various implementations vary greatly. In this section, we discuss basic concepts of OpenCL and the relevant limitations of the programming model.

#### Host-Run Code vs. Device-Run Code

The first important concept when implementing massively parallel programs is the distinction between host- and device-run code: while massively parallel programs are very well suited to perform computation- or bandwidth-intensive tasks, they are not a good match for control-heavy workloads. Since most programs involve both, control/administration-heavy as well as computation-heavy parts, massively parallel programming frameworks generally distinguish host-run code (for control-heavy parts) and device-run

```

1

typedef struct {unsigned int x,y;} spatialDataPoint;

2

typedef struct {spatialDataPoint low, high;} window;

3

4

__kernel void spatialSelectionScan(

5

const unsigned int tableCount,

__global spatialDataPoint* table.

7

const window query,

__global unsigned int *outputCounter,

8

9

__global spatialDataPoint *output){

10

11

const int i = get_global_id(0);

12

if(i < tableCount){</pre>

13

__private unsigned int x = clusterIndex[i].x;

__private unsigned int y = clusterIndex[i].y;

14

15

if (x \ge query.low.x && y \ge query.low.y &&

16

x <= query.high.x && y <= query.high.y){

17

output[atomic_inc(outputCounter)] = clusterIndex[i];

18

}

19

20

}

```

Figure 2.7: A Device-Run Selection Kernel implemented in OpenCL C

code (for computation-heavy parts). When implementing programs, the earlier is usually used to prepare and manage the execution of the later: allocate buffers, track operator dependencies and schedule the massively parallel parts for execution.

In OpenCL, the host-run code is implemented in regular ANSI C using a standardized function library that is part of the framework. The device-run code is implemented in OpenCL C. While OpenCL C can be used to implement conventional, i.e., sequential code that is to be run on the device, its most important use is to implement what is known as *Kernels*.

#### The Kernel Programming Model

The Kernel is arguably the most important concept in OpenCL: a Kernel is a function implemented in OpenCL C (a subset of ANSI C99). This function (see Figure 2.7 for an example) encapsulates the sequence of operations to be executed for a given "work item" (a single data element or iteration). The kernel code is compiled at runtime, transferred to the device as an executable binary and subsequently dispatched for execution. As apparent in Figure 2.7, the kernel does not contain code for memory allocation or the determining if the work is done. In fact, OpenCL C is restricted such that the language and standard function library simply do not contain functionality that cannot be executed efficiently on the targeted, i.e., massively parallel, hardware

All of these control operations are implemented and run on the host in ANSI C (see 2.8). We will, therefore, illustrate the limitations of the

```

1

cl_mem table = clCreateBuffer(getCLContext(),

2

CL_MEM_READ_ONLY,

3

inputSize, NULL, &err);

4

cl_event transferEvent;

5

cl_int clEnqueueWriteBuffer ( getCommandQueue(),

6

table, 0, 0, inputSize,

7

input, 0, NULL, transferEvent);

8

9

cl_mem output = clCreateBuffer(getCLContext(),

10

CL_MEM_READ_WRITE,

11

outputSize, NULL, &err);

12

13

cl_kernel selectKernel = clCreateKernel(

getProgram("spatialSelectionScanProgram"),

14

15

"spatialSelectionScan", &err);

16

17

18

clSetKernelArg(selectKernel, 1, sizeof(cl_mem), &table);

19

20

clSetKernelArg(selectKernel, 4, sizeof(cl_mem), &output);

21

22

cl_event completionEvent;

23

clEnqueueNDRangeKernel(

24

getCommandQueue(), selectKernel, 1, (const size_t[]) { 0 },

25

(const size_t[]) { ceil(tableCount / ((float)WORK_GROUP_SIZE))

26

* (WORK_GROUP_SIZE) },

(const size_t[]) { WORK_GROUP_SIZE }, 1, &transferEvent,

27

28

&completionEvent);

```

Figure 2.8: The (simplified) Host-Run Control Code of a Selection Kernel

massively parallel programming model by means of the limitations of the OpenCL C language and function library.

#### **Static Memory Allocation**

One of the most obvious limitations of OpenCL C is the lack of dynamic memory allocation: the OpenCL C standard function library does not contain a malloc function or any other function to reserve space in the GPU's internal memory. In order to reserve memory, the framework contains allocation functions to be run "statically" on the host, i.e., before dispatching the kernel for execution on the device. Lines 1 and 9 in Figure 2.8 show the allocation/creation of buffers in the device memory.

The impact of the restriction to "static" memory allocation varies: for selections the problem is somewhat manageable because the output is always smaller than the input, which gives a reasonable upper bound for the output size. It becomes a problem for operations such as joins for which tight bounds on the size of the output cannot be determined a priori: the upper bound for the output size of a join, i.e., the product of the joined relations, is large but rarely met. A common workaround is to to execute a join twice: once

to estimate the size of the output and a second time to actually produce the result [25]. Should the size of the output exceed the available storage, the authors propose to evaluate the joins in multiple passes which, naturally, increases the computational effort.

Even though the lack of memory reallocation is a problem it also has a significant performance advantage. Memory can be addressed using physical addresses, which eliminates the need for costly translation from virtual to physical addresses. In particular, this speeds up random memory accesses significantly.

#### A Priori Fixed Problem Size

Similar to input and output memory size, the problem size has to be specified up front. This is done by dispatching the kernel for execution on the device with the problem size as a parameter (line 25/26 in Figure 2.8). In many respects this is equivalent to a parallelized for-loop: The kernel is executed exactly n times in undetermined order with no opportunity to skip iterations, communicate among invocations or abort execution. In addition, OpenCL requires the number of iterations (the "global work size") to be a multiple of the degree of parallelism (the "local work size"). In the example, this is ensured by rounding up the global work size appropriately (in line 25 and 26).

Within each invocation, the kernel has access to an iterator variable (obtained using get\_global\_id in line 11 in Figure 2.7) that can be used to determine which piece of the work to do. While it is possible to execute all work in one complex iteration this reduces the degree of parallelism to one. This has a number of drawbacks: firstly, this limits the opportunities for latency hiding (see Section 2.1.4). Secondly, a single GPU computation unit is generally not powerful enough to max out the available memory bandwidth. It is, therefore, necessary to dissect a problem into as many independent pieces as possible when implementing an algorithm on a GPU.

#### Maximum Allocation/Mapping Size

Given the maximum size of the internal GPU memory, most GPUs use 32-bit (or even smaller) addresses for internal as well as external memory. To take it into account, the OpenCL standard defines a maximum size for a single allocation. The size is implementation specific and at least 128 MB. Whilst this ensures compatibility to low-end cards, it poses challenges when using the GPU for larger datasets: the data has to be sliced up into several buffers. Even though this is not a fundamental problem, it complicates the implementation and may induce buffer management overhead at runtime.

#### Single Instruction Multiple Threads

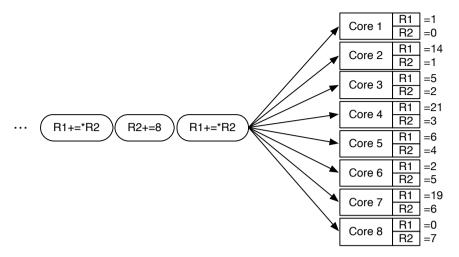

Whilst not strictly a problem of OpenCL, a GPU hardware peculiarity is the notion of SIMT (Single Instruction Multiple Threads). SIMT is the source

Figure 2.9: Single Instruction Multiple Threads

of a common misconception about GPU programming: even though a GPU supports many parallel threads, these are not fully independent as they are on a CPU. To clarify this, Figure 2.9 provides an illustration of the Single Instruction Multiple Threads (SIMT) paradigm: just like with conventional CPUs each of the computation cores executes exactly one thread using a set of operational registers (R1 & R2) that hold the thread's execution state. At every execution cycle, an instruction such as "read the value at address R2 and add it to R1" is dispatched and executed by every core on its own registers. In the Figure, the number of cores is eight while, in reality, multiples of 64 are usual. Thus, every scheduled instruction is executed at least 64 times (albeit on different data items/register states). A set of threads coupled like that is called a Work Group. Since threads within a work group have special properties such as cheaper synchronization, the Work Group concept is exposed to the programmer. In OpenCL, the programmer even can/has to configure the size of a work-group when scheduling a kernel for execution. While a small Work Group size is sometimes necessary, a work group of less than 64 items underutilizes the GPU's computation cores. Since all tasks in a Work Group are executed in the SIMT paradigm, the Work Group Size has a severe impact on branching: if one branch in a Work Group diverges from the others the branches are serialized and executed on all cores. The cores that execute a branch involuntarily are still occupied but do not write the results of their operations.

# Chapter 3

# Relational Data Management Systems

To manage is to forecast and plan, to organize, co-ordinate and to control.

Henri Fayol [26]

Data management is not a trivial task: reliable storage, persistent updates, effective multi-user operations and efficient analytics are just some of the requirements that must be met by a data management solution. To ease the burden on application developers, data management is mostly implemented in dedicated data management components/systems. These systems usually encapsulate the implementation of a logical data model implementing an internal storage and processing model. As logical data model, this thesis exclusively focuses on the Relational Data Model as defined by Edgar F. Codd [27]. The internal storage and processing model are degrees of freedom that a system can exploit to provide the aforementioned functionality. Consequently, these are also the parameters we will experiment with in the rest of this thesis. It is, therefore, prudent to precede the presentation of our contributions with a description of the state of the art in relational data storage and processing models as well as an overview of the most common method of selecting values for various tuning parameters: query cost modeling. This chapter is intended to provide enough background knowledge on relational data management to build on in the rest of this thesis. A discussion of recent related research is provide towards the end of this thesis in Chapter 8.

# 3.1 Relational Storage Models

As mentioned, the logical data model of relational data management systems is not open for change. For physical storage however there are several options, the choice of which has significant impact on data locality and, hence, system performance in different cases.

#### 3.1.1 N-ary Storage

Traditionally, relational tuples have been mapped to the one-dimensional memory strictly record-wise: all attributes of a tuple are written to a consecutive area in memory, one slot followed by the next [28]. In terms of data locality this means that there is high locality between the attributes of a tuple. Since increased locality generally leads to better performance, this storage scheme benefits applications that access many attributes of a tuple, i.e., transactional applications. The best representative of this class of applications is one that only performs (indexed) lookups of single tuples. In this case, the tuple can usually be accessed by accessing a single page.

Unfortunately, storing data according to this model means that the values of the same attribute but of different tuples are at least separated by the length of one tuple. The consequence is a very low degree of data locality for the values of an attribute. Analytical queries, that usually access values of few attributes but many tuples, are therefore executed on a suboptimal storage layout.

This effect has been recognized by database administrators who came up with a pragmatic optimization: since attribute values are separated by at least a tuple length the data locality between them can be increased by reducing the length of a tuple. This is usually achieved by (vertically) partitioning a table and using a surrogate primary key and foreign-key relationships between the partitions to maintain tuple integrity. In the most extreme case, every attribute is stored in exactly one partition: the data is stored according to the Decomposition Storage Model (DSM) [29].

# 3.1.2 (Fully) Decomposed Storage

While fully decomposed storage can be "simulated" using single-value partitions, surrogate primary keys and appropriate foreign-key constraints, this "hack" forfeits a number of optimizations that are possible if the storage structure was known at a lower layer of the DBMS architecture.

DSM has a major disadvantage: all queries that access more than one attribute have to reconstruct the logical tuples from the physical relations using a join on the surrogate primary key. While indices can be used to to speed up this tuple reconstruction, the costs for index storage, traversal and maintenance can be significant.

When implemented at the storage layer, however, it is possible to remove the explicit id and the needed index from the attribute's relation and use an implicit id that is calculated from the value's location (e.g.,  $id = \frac{address(value) - columnoffset}{sizeof(valuetype)}$ ). This reduces the tuple reconstruction costs to those of a (random) lookup (a.k.a. Invisible Join) and is therefore a very sensible optimization [30]. A database that stores all relations in Decomposed Storage Model (DSM) and performs the tuple reconstruction transparently in the storage layer is often called column-oriented [31] as opposed to row-oriented DBMSs that follow the N-ary storage model.

However, even when reconstructing tuples using positional lookups, the costs for tuple reconstruction can be significant: with n requested attributes, the system has to perform n (pseudo-)random accesses to the memory. Unless many tuples are requested and the values for their attributes are located on a single memory block this also results in n block accesses per tuple. If the value for an attribute only occupies a fraction of the block, transmitting the rest wastes memory bandwidth.

#### 3.1.3 Partially Decomposed Storage

As illustrated earlier, neither N-ary nor fully decomposed storage is optimal for all queries. A general guideline is that N-ary storage is preferable for transactional applications while decomposed storage favors analytical workloads. However, many applications do not clearly fall into one of these categories and some (like search) entirely defy this classification. Such mixed (OLTP/OLAP) workloads inspired the "hybrid" or, more accurately, the Partially Decomposed Storage Model (PDSM) [32]. In this model, database schemas are decomposed into (multi-attribute) partitions such that a given workload is supported optimally, i.e., data access locality is maximized. Naturally this introduces another degree of freedom in the database's design: the decomposition strategy. While the selection of the optimal decomposition strategy for a given workload, data and hardware configuration is far from trivial, the partially decomposed storage model promises optimal data locality for any given application.

# 3.2 Relational Processing Models

Just like the storage model, the processing model has been a subject to research: several paradigms have been proposed to implement a relational query processor. Each of these has strengths and weaknesses that make it suitable for different use cases.

# 3.2.1 Volcano-style Processing

One of the earliest relational query processing paradigms was developed and implemented as part of the Volcano system [33]. In Volcano, relational query plans are constructed from flexible operators that can change their behavior at runtime. When constructing the physical query plan, the operators are "configured" and connected by injecting function pointers (selection predicates, aggregation functions, etc.). Although multiple variants of this model exist, they all face the same fundamental problem: operators that can change their behavior at runtime are, from a CPU's point of view, unpredictable. This is a problem, because many of the performance optimizations of modern CPUs and compilers rely on predictable behavior (see Section 2.1.4 in Chapter 2). Unpredictable behavior circumvents these optimizations and causes hazards like pipeline flushing, poor instruction cache locality and limited

instruction level parallelism [34]. Therefore, flexible operators, as needed in Volcano-style processing, are usually CPU inefficient. Naturally, this is a problem in systems that expose the CPU as the main performance bottleneck. In convential, i.e., disk-based systems the costs are usually dominated by the disk accesses and can, thus, benefit from the simplicity and elegance of the Volcano approach without being limited by the (relatively) low CPU efficiency. With the transition to the much faster main-memory as primary storage medium, however, the CPU efficiency became the dominating factor [35]. This triggered research into CPU efficient processing models for relational data management systems. In the following, we will present some of the results of this research.

#### 3.2.2 Bulk Processing

The Bulk Processing Model is an approach to CPU efficient processing of relational data that focuses on analytical applications [36, 35]. Like in Volcano, complex queries are decomposed into precompiled primitives. However, Bulk Processing primitives are static loops without function calls that materialize all intermediate results [35]. For analytical applications on memory-resident data, the resulting materialization costs are outweighed by the savings in CPU efficiency. Efforts to reduce the materialization costs have led to the vectorized query processing model [37] which (bulk-)processes data in cache-sized chunks which constrains intermediate materialization to the CPU cache. This achieves CPU efficient processing without the need for expensive intermediate materialization into the main memory.

As mentioned, the *Bulk Processing Model* is focused on analytical applications and its implementations (MonetDB, Vectorwise, ...) naturally excel in this domain. However, the transaction processing performance of these systems is, again, dominated by CPU costs. This is due to the fact that the per-operator overhead (scheduling, loading, ...) is significantly higher than the costs for processing data in such scenarios. However, since transaction processing systems often execute the same query many times, much of the overhead can be amortized over the operators. Since (a priori) query compilation removes this per-query overhead, it is a reasonable means to reduce costs in a transactional system.

# 3.2.3 Query Compilation

(A priory) query compilation is advocated by, e.g., the VoltDB system [38] as a means to support high performance transaction processing on memory resident data. It achieves CPU efficiency, i.e., avoids function calls, by statically compiling queries to machine code and inlining functions. The processing model supports SQL for query formulation but needs a reassembly and restart of the system whenever a query is changed or added. It also complicates the optimization of complex queries, because all plans have to be generated without knowledge of the data or parameters of the query.

These factors make it unsuited for Online Analytical Processing (OLAP) applications that involve complex or ad-hoc queries.

A similar approach is implemented by the DBToaster [39] project as well as its intelectual spinn offs OCAS [40] and Legobase [41]. In each case, the queries are formulated in a high-level language and compiled into machine code. The high-level approach allows for efficient logical optimization while the generation of machine code yields runtime efficiency. Like VoltDB, however, these approaches involve significant compilation costs, making them unsuited for ad-hoc query processing.

#### 3.3 Cost Models

The goal of cost modeling is to estimate the costs of a given query before executing it. Since they form the basis for many optimizations, cost models are one of the most thoroughly studied fields in data management research. For completeness sake, we include a (literally copied [42]) overview of data management cost modeling research here.

Estimating the costs of a query is necessary for query as well as partial decomposition optimization. It is generally desirable to estimate the costs in a metric that has a total order (e.g., a simple integer value). This allows to compare two values in the metric and determine which one is "better". To calculate this value, the model may use a single [28, pgs. 441ff.] [43] or many intermediate metrics [44, 45]. The values for these metrics can be derived directly from the query, i.e., without taking the actual execution plan into account, the logical plan or the physical query plan. While the accuracy improves in this order, so does the cost estimation effort. We will discuss all of these approaches in the following.

### 3.3.1 Logical Cost Models

#### Estimating Costs directly from the Query

Data Morphing [46] is an approach to the partial decomposition problem that estimates the costs directly from the query. It relies on an input that specifies the percentage of the values that are accessed of every attribute. From that, the number of induced cache misses per tuple is estimated using a simple formula. To simplify the model, the authors make a number of assumptions:

- the values of all attributes are accessed in a uniform and random fashion,

- a read cache line is not removed from the processor cache before all the values in that cache line have been processed and

- all operations are executed on an empty cache

While these assumptions may hold for simple queries that can be evaluated in a single scan of attributes, it fails for complex queries that involve intermediate results or repetitive accesses to values (joins, group-bys, late materializing operators, ...).

#### Estimating Costs from the Operator Tree

To take intermediate results and repetitive accesses to values into account, a more accurate model of the evaluation of the query by the DBMS is needed. Since the relational operator tree is such a model, it can be used for a more accurate cost estimation. The estimation of query costs from the operator tree is similar to the evaluation of the tree: The costs of each executed operator are estimated (bottom up) and the overall costs of the query derived from that (usually by simply summing the costs of the operators [28]).

To estimate the costs of an operator it is necessary to know the number of tuples it has to process. Most operator-based cost models assume "a perfect oracle" [44] to estimate the number of input and output tuples.

This estimation is not trivial because it is influenced not only by the number of tuples in each relation, but also by the selectivity of the predicates that are used in the query. Substantial research exists on the estimation of predicate selectivity [47, 48, 46]. It is largely based on histograms, that represent the distribution of the values of an attribute. In this thesis we will assume that the values are distributed randomly and equally. This eliminates the need for histograms and reduces the needed statistical information to the number of unique values (cardinality) of each attribute. Incorporating more sophisticated selectivity estimation should be straight forward.

#### 3.3.2 Physical Cost Models

Disk-Based Cost Models do not in principle differ from main memory data access costs [49]. It is, therefore, reasonable to investigate into disk based cost models as well. Simple models [28, pages 439ff] [43] are solely based on the number of disk operations, i.e., the number of accessed blocks. They do not differentiate random and sequential access. Some (very simple) models [50, 51] only consider the number of accessed items without considering that two accesses might happen on the same block. Some models [49] only consider random misses (seeks), since they are much more costly than sequential misses (see Section 2.1.2). However, all of these models only consider a single layer, rendering them unfit to accurately predict access costs for memory-resident data. Models for main memory access cost have to distinguish random and sequential misses on multiple layers in the memory hierarchy [44].

Main-Memory Cost Models Listgarten and Neimat [52] differentiate Main-Memory Cost models into three categories: application-based, engine based and hardware-based.

Application based cost models estimate costs based on the limiting factor of each executed operator. Rules how to find the limiting factor are usually defined manually. E.g., join-performance may be limited by the memory access speed if the relations are large in relation to the available cache or limited by the processing speed if the joined relations fit into the cache. This makes application based cost models very unattractive because they are specific to the hardware and the implementation of the DBMS. Such a model is, e.g., used in [53].

Engine-based cost models focus on the properties of executed operations. Operations in this context are not hardware operations, like requesting an address or adding two values, but operations of the execution engine, like the comparison of two tuples or the output of a tuple. Such a model is introduced by Listgarten and Neimat in the same work [52]. Engine-based models are more generic than application-based models but still do not take parameters of the hardware into account.

The last category are hardware-based cost models. Execution costs are measured in the number and type of hardware operations. Since database performance is mainly determined by data access costs it is reasonable to only take data access operations into account. Such models are widely used [54, 44, 46] because they provide very generic models and good prediction performance.

# Chapter 4

# Exploiting Asymmetries in the Workload

Causa latet, vis est notissima. The cause is hidden, the effect most evident.

Ovid [55]

One of the fundamental requirements of a DBMSs is that data that is entered into the system is stored and accessible indiscriminately. However, this does not imply that all data items can be, or should be, treated equally: due to limited locality some data accesses are necessarily penalized with respect to others. By careful data placement, however, such penalties can be reduced significantly. Naturally, the optimal data placement strategy depends on a number of factors such as the employed hardware, the data and the workload.

When targeting memory resident databases, the most significant factor regarding data locality is the CPU's cache hierarchy. Substantial effort has been made by data management researchers to improve cache efficiency of data management operations. However, existing solutions often sacrifice an equally important resource in order to achieve cache conscious data processing: CPU cycles. In this section, we describe our efforts to develop a data storage/query processing scheme that provides cache conscious as well as CPU efficient data management.

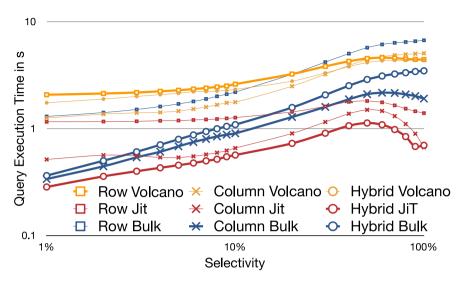

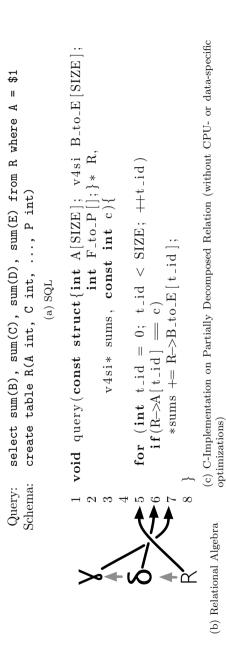

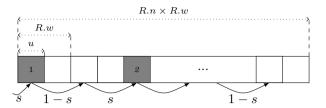

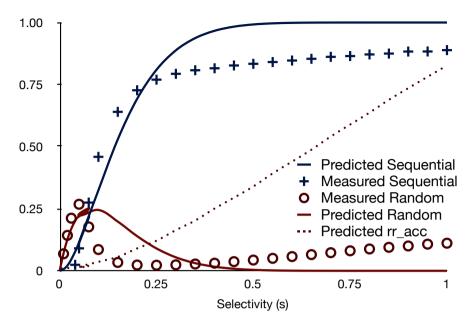

#### 4.1 Motivation