Exercises in parallel combinatorial computing

G.A.P. Kindervater

**Centrum voor Wiskunde en Informatica** Centre for Mathematics and Computer Science

1980 Mathematics Subject Classification: 90Cxx, 68A05, 68C25, 68Exx. ISBN 90 6196 400 8 NUGI-code: 811

Copyright  $\ensuremath{@}$  1991, Stichting Mathematisch Centrum, Amsterdam Printed in the Netherlands

### **CWI Tracts**

### **Managing Editors**

J.W. de Bakker (CWI, Amsterdam) M. Hazewinkel (CWI, Amsterdam) J.K. Lenstra (Eindhoven University of Technology)

#### **Editorial Board**

W. Albers (Enschede)

P.C. Baayen (Amsterdam)

R.C. Backhouse (Eindhoven)

E.M. de Jager (Amsterdam)

M.A. Kaashoek (Amsterdam)

M.S. Keane (Delft)

H. Kwakernaak (Enschede)

J. van Leeuwen (Utrecht)

P.W.H. Lemmens (Utrecht)

M. van der Put (Groningen)

M. Rem (Eindhoven)

H.J. Sips (Delft)

M.N. Spijker (Leiden)

H.C. Tijms (Amsterdam)

### CWI

P.O. Box 4079, 1009 AB Amsterdam, The Netherlands Telephone 31 - 20 592 9333, telex 12571 (mactr nl), telefax 31 - 20 592 4199

CWI is the nationally funded Dutch institute for research in Mathematics and Computer Science.

.

# CONTENTS

| ). Introduction                                                   | 1                |

|-------------------------------------------------------------------|------------------|

| Computational models     1.1. Taxonomy of Flynn                   | 3<br>3<br>5<br>8 |

| 1.2. Taxonomy of Schwartz                                         | 5                |

| 1.3. Control-driven, data-driven, and demand-driven architectures |                  |

| 1.4. Algorithms                                                   | 8                |

| 2. Parallel complexity                                            | 12               |

| 2.1. The parallel computation thesis                              | 12               |

| 2.2. Polylog parallel algorithms                                  | 15               |

| 2.3. \P-completeness                                              | 31               |

| 3. Experiments with fine-grained parallelism                      | 47               |

| 3.1. Architectures                                                | 49               |

| 3.2. Change making                                                | 55               |

| 3.3. Shortest paths                                               | 61               |

| 3.4. Knapsack                                                     | 65               |

| 4. Experiments with coarse-grained parallelism: branch and bound  | 70               |

| 4.1. Architectures                                                | 71               |

| 4.2. Traveling salesman                                           | 73               |

| 4.3. Job shop scheduling                                          | 75               |

| 4.4. Anomalous behavior                                           | 77               |

| 5. A queueing network model for distributed enumeration           | 81               |

| 5.1. Queueing model description                                   | 82               |

| 5.2. Mathematical analysis of the node processing mechanism       | 84               |

| 5.3. Numerical examples                                           | 91               |

| 5.4. The machine repair model                                     | 94               |

| 6. Perspectives                                                   | 99               |

| 6.1. Computational models                                         | 99               |

| 6.2. Architectures                                                | 100              |

| 6.3. Computations                                                 | 101              |

| References                                                        | 102              |

| Index                                                             | 109              |

# Introduction

Over the past 40 years, traditional sequential computers have become faster by a steady series of improvements of their individual components. Operating speeds of these machines are now approaching their physical limits. In spite of all the advances, however, there are still many problems which are unsolvable in reasonable time. Hence, more powerful architectures are required. A way to achieve further speedups is through the use of a collection of processors that cooperate in the solution process.

The first parallel computers were proposed in the late fifties. As in those days technological developments continued to improve the performance of traditional sequential machines enormously, the exploitation of parallelism in order to obtain faster computation times was generally regarded unnecessary. With the exception of the Illiac IV [Barnes, Brown, Kato, Kuck, Slotnick & Stokes 1968], no parallel computers were built. Around 1975, the situation changed: operating speeds of sequential computers became such high that a much improved performance could only be expected by invoking parallel computations. Since then, a diversity of parallel architectures has become available.

Operations research is one of the areas that are likely to benefit from advances in parallel computing. With respect to sequential computing, many operations research problems appear to be practically intractable, and for other problems a shorter solution time would be preferable. Today's parallel computers cannot solve all of these problems adequately either, but for future generations of parallel computers this may be different.

In this tract, we discuss some aspects of the impact of parallel computing on combinatorial operations research. In the first place, it is necessary to investigate what one can and cannot expect from parallelism. The complexity theory for parallel computations provides the means to achieve this. On the other hand, there exists a formidable gap between theoretical models for parallel

computing and existing machines, and, in addition, available architectures differ very much from each other. It is therefore of interest to see what the capabilities of the current generation of parallel computers are. In particular, we would like to find out what kinds of architecture are most suitable for the field of combinatorial optimization, and what techniques can be used.

The organization of this tract follows the structure of the survey papers [Kindervater & Lenstra 1986, 1988]:

Chapter 1 describes *machine models* for parallel computations. Machines can be classified according to *processor autonomy*, *interprocessor communication*, and *model of operation*. Examples of theoretical as well as realistic models are considered. The simulation of theoretical models by realistic ones is discussed.

Chapter 2 deals with the *complexity theory* for parallel computations. Given the basic distinction between *membership of*  $\mathfrak P$  and *completeness for*  $\mathfrak M \mathfrak P$  in sequential computing, we consider the speedups possible due to the introduction of parallelism. Within the class  $\mathfrak P$ , this leads to a distinction between 'very easy' problems, which are solvable in *polylogarithmic parallel time*, and the 'not so easy' ones, which are  $\mathfrak P$ -complete under log-space transformations. We will give examples of polylog parallel algorithms and discuss a number of  $\mathfrak P$ -completeness results. In particular, we will concentrate on the construction of traveling salesman tours by some well-known heuristics [Kindervater, Lenstra & Shmoys 1989], and on the iterative improvement of such tours by local search methods [Kindervater, Lenstra & Savelsbergh 1990].

Chapter 3 discusses the *implementation* of standard algorithms for the change-making, shortest paths and knapsack problems on parallel computers that are suited for algorithms that make use of *fine-grained* parallelism; it is based on Kindervater & Trienekens [1988].

Chapter 4 analyzes the *coarse-grained* parallelization of *branch and bound* methods at the level of the parallel evaluation of nodes in the search tree. We describe experiments with branch and bound algorithms for the traveling salesman and the job shop scheduling problems. The *anomalous behavior* that these methods sometimes exhibit, is discussed in the last section of this chapter.

Chapter 5 gives a first attempt to the design and analysis of a model for the distribution of a tree search procedure over several parallel processors. A queueing network approach is taken to describe the various processes in a master-slave environment [Boxma & Kindervater 1991].

Chapter 6, finally, addresses issues that withstand a real breakthrough of parallel computing: the *diversity* among existing parallel architectures as well as the wide *gap* between theoretical models and available computers. It will also be necessary to develop formal techniques for the design and implementation of efficient parallel partitioning and tree search methods [Kindervater, Lenstra & Rinnooy Kan 1989].

The area of parallel computing is expanding very fast. It could have a beneficial influence on operations research. The current situation is chaotic, however, and it is not as yet clear where it will lead to. In this tract, we discuss current developments and offer some suggestions of what would be desirable from an operations research point of view.

# Computational Models

Many architectures for parallel computations have been proposed in the literature. A number of these machines actually exist or are being built. Unfortunately, parallel computers differ very much from each other, and the performance of algorithms is therefore highly architecture dependent. Accordingly, there exists no general theoretical model that effectively describes the broad spectrum of feasible parallel architectures. Some theoretical models are useful for the design and analysis of parallel algorithms, but their realization is usually not feasible due to physical limitations.

In the next sections, we will discuss three ways of classifying parallel architectures. The classifications are more or less orthogonal to each other and are based on *processor autonomy*, *interprocessor communication*, and *model of operation*. We end this chapter by describing a number of algorithms that illustrate the use of some specific architectures. Unless otherwise stated, a brief description of the parallel computers mentioned below can be found in Dongarra & Duff [1985].

### 1.1. TAXONOMY OF FLYNN [1966]

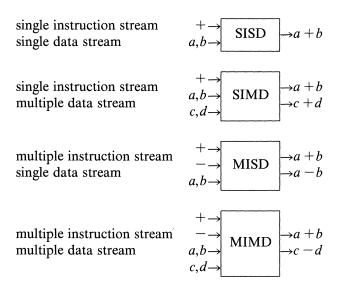

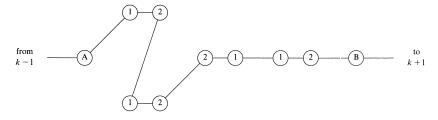

The most widely used classification of parallel computers is due to Flynn. Flynn distinguishes four classes of machines (cf. Figure 1.1).

- (1) SISD (single instruction stream, single data stream). One instruction is performed at a time, on one set of data. This class contains the traditional sequential computers.

- (2) SIMD (single instruction stream, multiple data stream). One type of instruction is performed at a time, possibly on different data. An enable/disable mask selects the processing elements that are allowed to perform the operation on their data. The ICL(AMT)/DAP (Distributed Array Processor) (see Section 3.1.1), the Goodyear/MPP (Massively Parallel

FIGURE 1.1. The classification of Flynn.

Processor) and the Connection Machine belong to this class. Also, *vector* computers such as the Cray-1 and the CDC/Cyber-205 (see Section 3.1.2) are often considered as SIMD machines.

In vector machines, an arithmetic operation is performed by a functional unit. The operation is split into a chain of small tasks. Each component of the functional unit performs a specific task and passes the result to its neighbor. The computation is sped up by the *pipelining* of independent operations of the same type: as soon as a component has completed a task, it is ready to start the same task of the next operation. It turns out that developing algorithms for vector computers and SIMD machines can be done along the same lines.

- (3) MISD (multiple instruction stream, single data stream). Different instructions on the same data can be performed at a time. This class has received very little attention so far.

- (4) MIMD (multiple instruction stream, multiple data stream). Different instructions on different data can be performed at a time. There are two types of MIMD computers: the processors of a synchronized MIMD machine perform each successive set of instructions simultaneously; the processors of an asynchronous MIMD machine run independently and wait only if information from other processors is needed. The Alliant/FX8, the BBN/Butterfly, the IBM/LCAP (Loosely Coupled Array of Processors) (see Section 4.1.1) and the Intel/iPSC (Intel's Personal SuperComputer) are examples of MIMD machines.

If one considers the many types of algorithms that are suitable for execution on parallel computers, then both ends of the spectrum can be characterized in a way that resembles the above distinction between the two types of MIMD machines. *Systolic* algorithms lead to highly synchronized computations, where

Computational models 5

the processing elements act rhythmically on regular streams of data passing through the (SIMD or synchronized MIMD) machine. Typical examples are the algorithms to be presented in Section 1.4 and the dynamic programming recursions in Chapter 3. *Distributed* algorithms lead to asynchronous processes, in which the processors perform their own local computations and communicate by sending messages every now and then. Branch and bound (see Chapter 4) lends itself to this approach.

# 1.2. TAXONOMY OF SCHWARTZ [1980]

Flynn's classification is not concerned with the way in which information is transmitted between the processors. This is dealt with by Schwartz, who distinguishes between paracomputers and ultracomputers.

In a paracomputer, the processors have simultaneous access to a shared memory, which allows for communication between any two processors in constant time. A further distinction is based on the way in which shared memory computers handle read and write conflicts, which occur when several processors try to read from or to write into the same memory location at the same time. Paracomputers help us in investigating the intrinsic parallelism in problems and algorithms. They are therefore of great theoretical interest, but current technology prohibits their realization. In many existing architectures, the processors have access to a common memory. As these machines only approximate a real shared memory by handling read and write instructions sequentially, they cannot be considered as paracomputers.

The most common paracomputer model is the PRAM (Parallel Random Access Machine). The PRAM is a synchronized MIMD machine with an unbounded number of processors and a shared memory, which allows simultaneous reads from the same memory location but disallows simultaneous writes into the same memory location. The computation starts with one processor activated; at any step, an active processor can do a standard operation or activate another processor; and the computation stops when the initial processor halts.

In an *ultracomputer*, each processor has its own memory and the processors communicate through a fixed *interconnection network*. Such a network can be viewed as a graph with vertices corresponding to processors and (undirected) edges or (directed) arcs to interconnections. Two parameters of the graph are important in this context: the maximum vertex degree  $d_1$ , which should be bounded by a constant on grounds of practical feasibility, and the maximum path length  $d_2$  (the 'diameter'), which should grow at most logarithmically in the number p of processors to ensure fast communication.

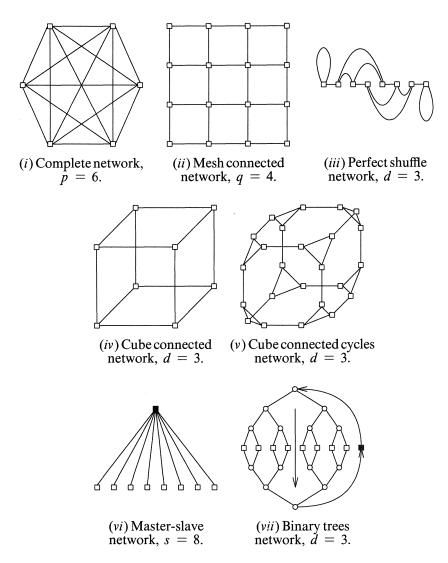

Of the many interconnection networks that have been proposed, seven are briefly described below. They are illustrated in Figure 1.2.

(i) Complete network. Each pair of processors is directly connected. In a p-processor system,  $d_1 = p - 1$  and  $d_2 = 1$ . An example of this type of configuration is the MPC (Module Parallel Computer). The MPC is a theoretical model, in which each processor has its own memory and is connected to all other processors. By sending messages, a processor can access a variable stored

FIGURE 1.2. Seven interconnection networks.

in the memory of another processor. However, if several processors try to access a variable stored in the memory of the same processor simultaneously, only one will succeed and the others receive a message that the access failed.

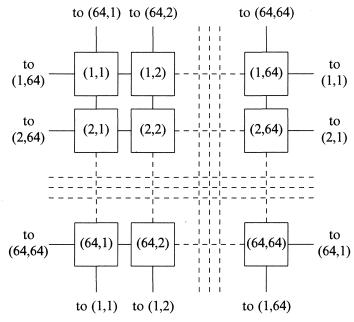

(ii) Two-dimensional mesh connected network [Unger 1958]. Each processor is identified with an ordered pair (i,j) (i,j=1,...,q), and processor (i,j) is connected to processors  $(i\pm 1,j)$  and  $(i,j\pm 1)$ , provided they exist. Note that  $d_1=4$  and  $d_2=2(q-1)=\Theta(\sqrt{p})$ . This interconnection network is used in the ICL(AMT)/DAP and the Goodyear/MPP.

Computational models 7

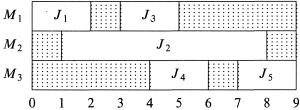

(iii) Perfect shuffle network [Stone 1971]. There are  $p=2^d$  processors with interconnections (i, 2i-1), (i+p/2, 2i), (2i-1, 2i) for i=1,...,p/2. The first two types of interconnections imitate a perfect shuffle of a deck of cards. We have  $d_1=3$  and  $d_2=2d-1=\Theta(\log p)$ .

- (iv) Cube connected network [Squire & Palais 1963]. This can be seen as a d-dimensional hypercube with  $2^d$  processors at the vertices and interconnections along the edges. Note that  $d_1 = d_2 = d = \log p$ . The Intel/iPSC and the Connection Machine are organized this way.

- (v) Cube connected cycles network [Preparata & Vuillemin 1981]. This is a cube connected network with each of the  $2^d$  processors replaced by a cyclicly connected set of d processors; each of them has two cycle connections and one edge connection. This yields  $d_1 = 3$  and  $d_2 = \Theta(\log p)$ .

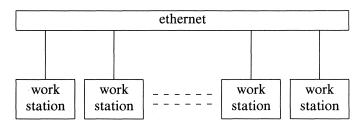

- (vi) Master-slave network. There are s+1 processors, organized as a one-level tree: one 'master' processor is connected to s 'slave' processors. Note that  $d_1 = s$  and  $d_2 = 2$ . As an example we have the IBM/LCAP.

- (vii) Binary trees network [Bentley & Kung 1979]. There are  $p = 3 \cdot 2^d 2$  processors, interconnected by two binary trees with common leaves. The  $2^d$  processors corresponding to these leaves perform the actual computations. The other  $2^d 1$  processors in the first tree (an out-tree) send the data down to their descendants, and those in the second tree (an in-tree) combine the results from their ancestors. An additional master processor controls the network by providing the input for one root and receiving the output from the other. Note that  $d_1 = 3$  and  $d_2 = \Theta(\log p)$ .

All these networks can simulate each other quite efficiently; see Siegel [1977, 1979] for details. Still, it appears that the cube connected cycles and perfect shuffle networks are reasonably flexible, while the mesh connected and binary trees networks have been designed for more restricted types of computations.

Simulation of the theoretical PRAM model by ultracomputers with a bounded degree network that allows for fast communication is usually done in two phases:

First, the use of the shared memory is eliminated. An n-processor MPC can simulate a computational step of an (n,m)-PRAM (a PRAM with n processors and a shared memory of size m) with high probability in time  $O(\log n)$  [Upfal 1984] or in deterministic time  $O(\log m)$  [Alt, Hagerup, Mehlhorn & Preparata 1987]. The proof of the probabilistic bound is constructive, but for the deterministic simulation only an existence proof is given. The problem of finding a constructive deterministic simulation of a PRAM step in logarithmic time is still open.

The second phase eliminates the use of the complete interconnection network. One step of an n-processor MPC can be simulated in  $O(\log n)$  steps by a bounded degree network with n processors [Alt, Hagerup, Mehlhorn & Preparata 1987].

Combining the two phases, we conclude that a step of an (n,m)-PRAM requires probabilistic time  $O(\log^2 n)$  or deterministic time  $O(\log m \log n)$  on a bounded degree network.

Karlin & Upfal [1988] describe a direct simulation of a PRAM. They show that T steps of an (n,m)-PRAM can be simulated in  $O(T\log m)$  steps by a bounded degree network, with probability tending to 1 as n or T goes to infinity. Until today, no deterministic simulation with the same time characteristic is known.

# 1.3. Control-driven, data-driven and demand-driven architectures [Treleaven, Brownbridge & Hopkins 1982]

Parallel computers not only differ in the autonomy of the processing elements and the interprocessor communication, but also in the model of operation they use.

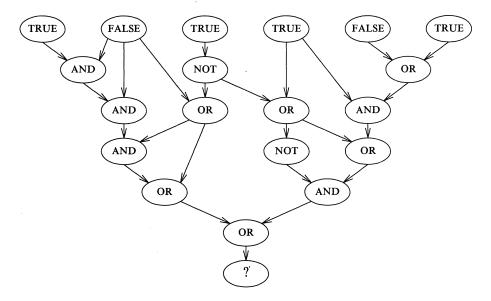

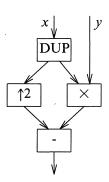

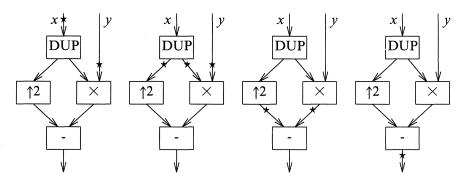

The main operational models are *control-driven*, *data-driven* and *demand-driven*. In control-driven architectures, the user specifies through his program the exact order in which the computations must be performed and also which operations are to be performed in parallel. In the data-driven model, an operation can be performed as soon as all its operands are available, and in the demand-driven model, an operation can be initiated as soon as its outcome is needed. In these last two models, the order in which operations are performed is completely determined by the program itself at run time. If we look at parallel processing as a multiple processor scheduling problem with precedence constraints where the statements of a program are the jobs and the dependencies of the statements are the precedence constraints, a data-driven computation corresponds in it most ideal form to the ordering of the statements according to the earliest-time scheduling algorithm, whereas a demand-driven architecture considers the statements according to the latest-time scheduling algorithm; cf., for example, Gondran & Minoux [1984].

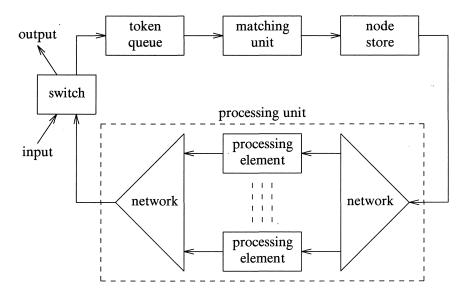

All sequential computers use the control model of operation and, at present, most of the existing parallel computers - including the ones mentioned in the previous sections - also use this method. A number of data-driven computers, called dataflow machines, have been built, but these machines are still in their infancy; see, for example, Watson [1984]. We will discuss the Manchester dataflow machine in Section 3.1.3 in detail. Demand-driven architectures do not yet exist. Several proposals have been made, such as the ALICE machine at the Imperial College in London [Darlington & Reeve 1981].

### 1.4. ALGORITHMS

As an illustration of the concepts defined above, we will end this chapter by giving some examples of parallel algorithms for elementary problems. They all use the control-driven model of operation and are developed for a specific type of interconnection network.

The quality of the parallelization of an algorithm will be judged on the resulting *speedup*, which is the running time of the best sequential implementation of the algorithm divided by the running time of the parallel implementation using p processors, and the *processor utilization*, which is the speedup divided by p. The best one can hope to achieve is a speedup of p and a processor utilization of 1. Note that these concepts are defined here relative to a

Computational models 9

given algorithm, irrespective of the possible existence of more efficient sequential algorithms for the problem at hand.

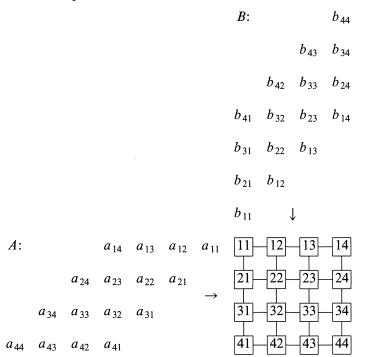

### 1.4.1. Matrix multiplication

Two  $n \times n$  matrices  $A = (a_{ij})$  and  $B = (b_{ij})$  can be multiplied in O(n) time on an  $n \times n$  mesh connected network. The basic idea is the use of the skewed input scheme illustrated in Figure 1.3. At each step of the computation, matrix A makes one step to the right, matrix B goes one step down, and each processing element (i,j) multiplies its current values  $a_{ik}$  and  $b_{kj}$  and adds the result into its accumulator (which starts at 0). It is easily verified that after 2n-1 stages processor (i,j) contains the required value  $\sum_k a_{ik} b_{kj}$  and that the procedure is best possible in terms of speedup and processor utilization. Furthermore, only one copy of each matrix element has to be kept in storage. This is a typical example of a systolic algorithm performed on an SIMD machine and suitable for VLSI implementation.

FIGURE 1.3. Matrix multiplication on a mesh connected network.

# 1.4.2. Transitive closure [Guibas, Kung & Thompson 1979]

The transitive closure of a directed graph G has an arc (i,j) if and only if G has a path from i to j. If G has n vertices, the algorithm from Section 1.4.1 can be applied to find the transitive closure in O(n) time using  $n^2$  mesh connected processors. Starting with A given by the adjacency matrix of G (i.e.,  $a_{ij} = 1$  if G has an arc (i,j) and  $a_{ij} = 0$  otherwise) and B = A, one executes the matrix

multiplication algorithm *three times*, with the modifications that addition is replaced by maximization and that any element  $a_{ij}$  or  $b_{ij}$  that passes through processor (i,j) is updated with the value of the accumulator. A correctness proof of this procedure can be found in the above reference.

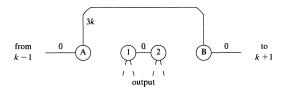

### 1.4.3. Membership testing

Given a set S of n elements and an element e, one can test whether  $e \in S$  in  $O(\log n)$  time on a binary trees network with  $d = \lceil \log n \rceil$ . Denote the processors corresponding to the common leaves by  $P_i$  ( $i = 1,...,2^d$ ) and suppose that  $P_i$  stores the ith element  $e_i$  of S ( $i \le n$ ). It takes d steps for the processors in the top tree to send e down, one step for the  $P_i$ 's to check whether  $e_i = e$ , and d steps for the processors in the bottom tree to compute the disjunction of the results.

As an extension, one can test the membership of S for m elements  $e^{(1)},...,e^{(m)}$  in  $O(m + \log n)$  time by pipelining the flow of information through the network. As soon as  $e^{(1)}$  leaves the first processor,  $e^{(2)}$  is sent to it; and, in general, at each step all data are going down one level.

By asking the processors in the bottom tree to do a bit more than computing logical disjunctions, one can use the same model to *find the minimum* of n elements and to *compute the rank* of a given element in  $O(\log n)$  time. We leave details to the reader.

# 1.4.4. Minimum spanning tree [Bentley 1980]

Given a complete undirected graph G with vertex set  $\{1,...,n\}$  and a length  $c_{ij}$  for each edge  $\{i,j\}$ , a spanning tree of G of minimum total length can be found in  $O(n^2)$  time by an algorithm from Prim [1957] and Dijkstra [1959]. The algorithm is based on the following principle. Let T(V) be the collexion of edges in a minimum spanning tree of the subgraph of G induced by the subset V of vertices. If  $i^* \notin V$  and  $j^* \in V$  are such that  $c_{i^*j^*} = \min_{i \notin V, j \in V} \{c_{ij}\}$ , then  $T(V \cup \{i^*\}) = T(V) \cup \{\{i^*, j^*\}\}$ .

The algorithm starts with  $T(\{1\}) = \emptyset$ . At each iteration, a minimum spanning tree on a certain vertex set V with edge set T(V) has been constructed and, for each  $i \notin V$ , a 'closest tree vertex'  $j_i \in V$  and a corresponding distance  $l_i$  are known, i.e.,  $l_i = c_{ij_i} = \min_{j \in V} \{c_{ij}\}$ . One selects an  $i^* \notin V$  for which  $l_{i^*} = \min_{i \notin V} \{l_i\}$ , adds  $i^*$  to V and  $\{i^*, j_{i^*}\}$  to T(V), and updates the values  $j_i$  and  $l_i$  for the remaining vertices  $i \notin V$ . There are n-1 iterations, each requiring O(n) time.

It is not hard to implement the algorithm on a binary trees network with  $d = \lceil \log n \rceil$ . The master processor stores the set T of spanning tree edges. Processor  $P_i$  keeps track of  $j_i$  and  $l_i$  and is able to compute any  $c_i$  in constant time. Each command that is sent down the tree is executed only by those  $P_i$ 's that are turned on.

We initialize by setting  $T = \emptyset$  and, for i = 2,...,n, turning on  $P_i$  and setting  $j_i = 1$  and  $l_i = c_{i1}$ . In each of the n-1 iterations, we first apply the minimum-finding procedure to determine  $i^*$  and add  $\{i^*,j_{i^*}\}$  to T; we next send  $i^*$  down in order to turn off  $P_{i^*}$  forever (since now  $i^* \in V$ ) and to turn off

Computational models 11

each  $P_i$  with  $l_i \le c_{ii^*}$  temporarily for the rest of this iteration (since no update is necessary); and we finally instruct all remaining  $P_i$ 's to set  $j_i = i^*$  and  $l_i = c_{ii^*}$ .

Since each iteration takes  $O(\log n)$  time, this parallel version of the algorithm has a running time of  $O(n\log n)$  using O(n) processors and hence a processor utilization of only  $O(1/\log n)$ . We cannot improve on this by pipelining the loop, since each iteration needs information from the previous one. However, we can use a smaller network with  $d = \lceil \log(n/\log n) \rceil$ , in which each  $P_i$  takes care of  $\lceil \log n \rceil$  vertices and performs all computations for them sequentially. This modified algorithm still runs in  $O(n\log n)$  time, but now using  $O(n/\log n)$  processors with a processor utilization of  $\Theta(1)$ .

The complexity theory for parallel computations explores the potential power and the inherent limitations of parallel computers. Section 2.1 presents an informal introduction to those concepts from the complexity theory for parallel computations that may have some impact on the field of combinatorial optimization. It turns out that parallelism introduces a distinction within the class  $\mathfrak{P}$ : many problems in  $\mathfrak{P}$  are solvable in *polylog parallel time*, and others can be shown to be  $\mathfrak{P}$ -complete under log space transformations. Examples of polylog parallel algorithms are given in Section 2.2, and a number of  $\mathfrak{P}$ -completeness results are discussed in Section 2.3.

### 2.1. The parallel computation thesis

Complexity theory deals with the classification of problems based on the *running time* and the *work space* required by algorithms for their solution. When considering parallel algorithms, we can also take the *number of processors* into account. Although the complexity theory has been developed for *decision* problems (i.e., problems that produce a 'yes' or 'no' answer), this is not a severe restriction, since most other problems can be reformulated in terms of a limited series of decision problems. An optimization problem, for example, can be solved by posing questions on the existence of a feasible solution with at most or at least a specified value.

In this section, we discuss the complexity theory for parallel computations as far as it is of importance to the theory of combinatorial optimization. We do not intend to go into much detail, and refer to Cook [1981] for a more thorough exposition. First, we review the complexity theory with respect to sequential computations (cf. Garey & Johnson [1979]).

Sequential computers are reasonably represented by models of computation such as the Turing machine and the random access machine (RAM). Given:

these models, we can define several complexity classes. The class  $\mathfrak P$  contains the problems that are solvable in *polynomial time*, i.e., the running time is bounded by a polynomial in the problem size. The problems in  $\mathfrak P$  are often called *well solved* or *easy*.  $\mathfrak PSPACE$  contains the problems that are solvable using *polynomial space*, i.e., the work space is bounded by a polynomial in the problem size. A very well studied class included in  $\mathfrak PSPACE$  is  $\mathfrak TP$ , the class of problems for which a feasible solution can be recognized as such in polynomial time. It is obvious that  $\mathfrak P \subseteq \mathfrak TP \subseteq \mathfrak PSPACE$ , and it is conjectured that both these inclusions are proper.

Another class contained in  $\mathfrak{P}SPACE$ , which has not attracted much attention with respect to sequential computations, is POLYLOGSPACE. It consists of the problems that are solvable in *polylog space*, i.e., work space that is polynomially bounded in the logarithm of the problem size. Many problems in  $\mathfrak{P}$  belong to POLYLOGSPACE, but it is generally believed that  $\mathfrak{P} \not\subseteq POLYLOGSPACE$ . We do know, however, that POLYLOGSPACE  $\neq \mathfrak{P}SPACE$ .

The classes PSPACE and MP have their complete members. The PSPACE-complete problems are generalizations of all other problems in PSPACE in terms of transformations that require polynomial time. More precisely: a problem is PSPACE-complete under polynomial-time transformations if it belongs to PSPACE and if any other problem in PSPACE is reducible to it by a transformation that requires polynomial time. It follows that, if any PSPACE-complete problem can be shown to belong to P, then PSPACE = P. Since this equality is not believed to be true, a polynomial-time algorithm for a PSPACE-complete problem is very unlikely to exist. For the class MP and its complete members, the same properties hold.

$\mathfrak P$  also has its complete problems. The  $\mathfrak P$ -complete problems generalize all other problems in  $\mathfrak P$  in terms of transformations that require logarithmic work space. Formally: a problem is *log space complete for*  $\mathfrak P$  or, better,  $\mathfrak P$ -complete under log-space transformations, if it belongs to  $\mathfrak P$  and if any other problem in  $\mathfrak P$  is reducible to it by a transformation using logarithmic work space. If any  $\mathfrak P$ -complete problem would belong to POLYLOGSPACE, then  $\mathfrak P \subseteq \mathsf{POLYLOGSPACE}$ . As this inclusion is believed to be false, an algorithm for a  $\mathfrak P$ -complete problem that uses only polylogarithmic work space cannot be expected.

Sequential and parallel computations are related by a hypothesis known as the parallel computation thesis [Chandra, Kozen & Stockmeyer 1981; Goldschlager 1982]: time bounded parallel machines are polynomially related to space bounded sequential machines. That is, for any function T of the problem size n, the class of problems solvable by a machine with unbounded parallelism in time  $T(n)^{O(1)}$  (i.e., polynomial in T(n)) is equal to the class of problems solvable by a sequential machine in space  $T(n)^{O(1)}$ . This thesis is a theorem for many 'reasonable' parallel machine models and 'well-behaved' time bounds; see Van Emde Boas [1985] for a survey. Fortune & Wyllie [1978], for example, showed that the class of problems solvable in  $T(n)^{O(1)}$  time by a PRAM is equal to the class of problems solvable in  $T(n)^{O(1)}$  work space by a Turing machine, if  $T(n) \ge \log n$ .

As a consequence, the class of problems solvable by a PRAM in polynomial

time is equal to PSPACE. Since the PRAM is able to solve the apparently difficult problems in PSPACE (such as the PSPACE-complete and PSP-complete ones) in polynomial time, it is obviously an extremely powerful model. The theorem by Fortune & Wyllie also implies that the problems in POLYLOGSPACE are exactly the ones solvable by a PRAM in *polylog parallel time*, i.e., in time that is polynomially bounded in the logarithm of the problem size. This leads to a distinction within the class P.

The problems in  $\mathfrak{P}$  belonging to POLYLOGSPACE are solvable in polylog parallel time. They can be considered to be among the *easiest* problems in  $\mathfrak{P}$ , in the sense that the influence of problem size on solution time has been limited to a minimum. (It should be noted here that a further reduction to sublogarithmic solution time is generally impossible. One reason for this is that a PRAM needs  $O(\log n)$  time to activate n processors; a similar reason is that in any realistic model of parallelism a constant upper bound on the maximum 'fan-out'  $d_1$  implies a logarithmic lower bound on the minimum 'communication time'  $d_2$ . See also Munro & Paterson [1973])

On the other hand, the  $\mathfrak{P}$ -complete problems are unlikely to admit solution in polylog parallel time. If any such problem would be solvable in polylog parallel time, it would belong to POLYLOGSPACE, and it would follow that  $\mathfrak{P} \subseteq \text{POLYLOGSPACE}$ . Hence, a solution in polylog parallel time is not expected. Any solution method for these *hardest* problems in  $\mathfrak{P}$  is likely to require superlogarithmic time and is therefore, loosely speaking, probably 'inherently sequential' in nature. This does not imply, of course, that parallelism cannot yield substantial speedups.

As a result, we can distinguish within  $\mathfrak{P}$  between the 'very easy' problems, which are solvable in polylog parallel time, and the 'not so easy' ones, for which such a speedup due to parallelism is unlikely.

The picture of the PRAM model as sketched above is in need of some qualification. The model is theoretically very useful, but its unbounded parallelism is hardly realistic. The reader will have no difficulty in verifying that a PRAM is able to activate a superpolynomial number of processors in subpolynomial time. If a polynomial time bound is considered reasonable, then certainly a polynomial bound on the number of processors should be imposed. It is a trivial observation, however, that the class of problems solvable if both bounds are respected is simply equal to  $\mathfrak{P}$ . Within this more reasonable model,  $\mathfrak{PP}$ -complete and  $\mathfrak{PSPACE}$ -complete problems remain as hard as they were without parallelism.

Discussions along these lines have led to the consideration of *simultaneous* resource bounds and to the definition of new complexity classes. For example, Nick (Pippenger)'s Class  $\Re C$  contains all problems solvable in polylog parallel time on a polynomial number of processors, and Steve (Cook)'s Class  $\Re C$  contains all problems solvable in polynomial sequential time and polylog space. Some sort of extended parallel computation thesis might suggest that  $\Re C = \Re C$ . This is a major unresolved issue in complexity theory, and outside the scope of this review. We refer to Johnson [1983] for further details and more references.

#### 2.2. POLYLOG PARALLEL ALGORITHMS

The polylog parallel algorithms described below are designed to run on the PRAM model or on an SIMD machine with a shared memory. Simultaneous writes into the same memory location are prohibited. The simultaneous reads that occur are not essential and can be eliminated. We will use the notation

to denote that the statement S(i) is to be executed in parallel for all values of i satisfying the condition B(i).

In some examples, we will encounter *randomized* algorithms, i.e., algorithms that produce the correct answer with probability greater than .5. From the complexity theory for randomized computations we only mention the class  $\mathfrak{RNC}$ , i.e., the class of decision problems solvable by a randomized algorithm in polylog time on a polynomial number of processors.

We note that the (randomized) algorithms to be presented below require a polynomial number of processors, so that the related decision problems belong to (R)NC.

### 2.2.1. Maximum finding

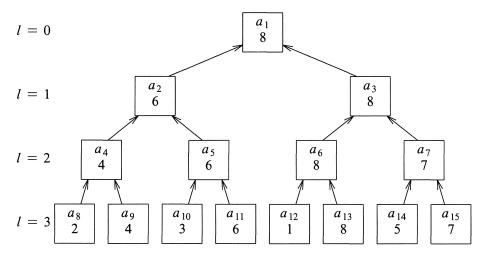

Given n numbers, one wishes to find their maximum. We assume, for convenience, that  $n = 2^m$  for some integer m and that the numbers are given by  $a_n, a_{n+1}, ..., a_{2n-1}$ . Consider the following procedure:

$$\begin{array}{ll} \text{for } l \!\leftarrow\! m-1 \text{ downto } 0 \text{ do} \\ \text{par } [2^l \!\leqslant\! j \!\leqslant\! 2^{l+1}-1] \ a_j \!\leftarrow\! \max\{a_{2j}, a_{2j+1}\}. \end{array}$$

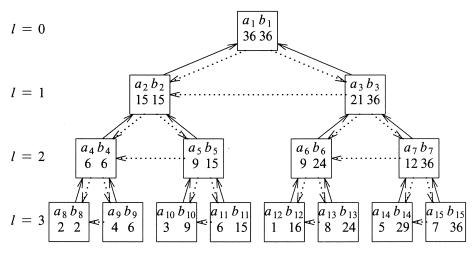

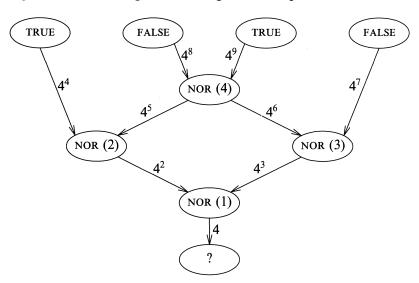

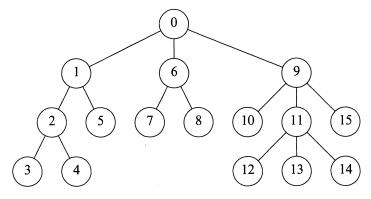

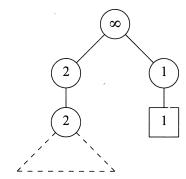

The computation is illustrated by means of a binary tree in Figure 2.1. At step l, the values corresponding to the nodes at level l of the tree are calculated. At the end,  $a_1$  is equal to the desired maximum.

FIGURE 2.1. Maximum finding: an instance with n = 8.

The algorithm requires  $O(\log n)$  time and n/2 processors. We can improve on this by applying a device similar to the one used in the last paragraph of Section 1.4.4. Suppose there are p ( $p \le n/2$ ) processors available, to which we assign n/p data. (For simplicity, we assume that p divides n.) Each processor first computes the maximum of the data assigned to it sequentially, before the above procedure is executed. The resulting algorithm has a running time of  $O(n/p + \log p)$  with p processors. For  $p = \lceil n/\log n \rceil$ , this provides an algorithm that runs in  $O(\log n)$  time, but now using only  $\lceil n/\log n \rceil$  processors with a processor utilization of  $\Theta(1)$ .

### 2.2.2. Partial sums [Dekel & Sahni 1983a]

Given *n* numbers  $a_n, a_{n+1}, ..., a_{2n-1}$  with  $n = 2^m$ , one wishes to find the partial sums  $a_n + ... + a_{n+j}$  for j = 0, ..., n-1. Consider the following procedure:

```

for l \leftarrow m-1 downto 0 do

par [2^l \le j \le 2^{l+1}-1] a_j \leftarrow a_{2j} + a_{2j+1};

b_1 \leftarrow a_1;

for l \leftarrow 1 to m do

par [2^l \le j \le 2^{l+1}-1] b_j \leftarrow if j odd then b_{(j-1)/2} else b_{j/2} - a_{j+1}.

```

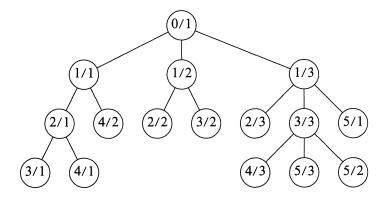

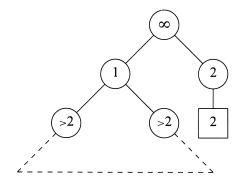

The computation is illustrated in Figure 2.2. In the first phase, represented by the solid arrows, the sum of the  $a_j$ 's is calculated in the same way as their maximum was calculated in Section 2.2.1. Note that the a-value corresponding to a non-leaf node is set equal to the sum of all a-values corresponding to the leaves descending from that node. In the second phase, represented by the dotted arrows, each parent node sends a b-value (starting with  $b_1 = a_1$ ) to its children: the right child receives the same value, the left one receives that value minus the a-value of the right child. The b-value of a certain node is therefore equal to the sum of all a-values of the nodes of the same generation, except those with a higher index. This implies, in particular, that at the end we have  $b_{n+j} = a_n + ... + a_{n+j}$  for j = 0,...,n-1.

The algorithm requires  $O(\log n)$  time and n processors. As before, this can be improved to  $O(\log n)$  time and  $O(n/\log n)$  processors.

Remark. In the form given above, the algorithm does not work for operations such as maximization. The partial sums algorithm uses subtraction, which has no equivalent in the case of maximization. We therefore present a version of the partial sums algorithm which is not quite so elegant as the original one, but which has the desired property since it makes use of addition only. It also runs in  $O(\log n)$  time using  $O(n/\log n)$  processors.

```

for l \leftarrow m-1 downto 0 do

par [2^l \leqslant j \leqslant 2^{l+1}-1] a_j \leftarrow a_{2j} + a_{2j+1};

for l \leftarrow 0 to m do

par [2^l \leqslant j \leqslant 2^{l+1}-1] b_j \leftarrow if j = 2^l then a_j else if j odd then b_{(j-1)/2} else b_{(j-2)/2} + a_j.

```

FIGURE 2.2. Partial sums: an instance with n = 8.

2.2.3. Sorting [Muller & Preparata 1975; Ajtai, Komlós & Szemerédi 1983] Given n numbers  $a_1,...,a_n$ , one wishes to renumber them such that  $a_1 \le ... \le a_n$ . We assume, for simplicity, that  $a_i \ne a_j$  if  $i \ne j$ . Consider the following procedure:

```

par [1 \le i, j \le n] \rho_{ij} \leftarrow if a_i \le a_j then 1 else 0;

par [1 \le j \le n] \pi_j \leftarrow \text{sum}\{\rho_{ij} \mid 1 \le i \le n\};

par [1 \le j \le n] a_{\pi_i} \leftarrow a_j.

```

The algorithm is based on *enumeration sort*: the position  $\pi_j$  in which  $a_j$  should be placed is calculated by counting the  $a_i$ 's that are no greater than  $a_j$ . There are three phases:

- (i) computation of the relative ranks  $\rho_{ij}$ :  $n^2$  processors, O(1) time or  $\lceil n^2 / \log n \rceil$  processors,  $O(\log n)$  time;

- (ii) computation of the positions  $\pi_j$ :  $n \lceil n/\log n \rceil$  processors,  $O(\log n)$  time (by application of the first phase of the algorithm of Section 2.2.2);

- (iii) permutation: n processors, O(1) time.

The algorithm requires  $O(\log n)$  time and  $O(n^2/\log n)$  processors. Simultaneous reads occur in the first phase, but there is a way to avoid them within the same time and processor bounds. As sequential enumeration sort takes  $O(n^2)$  time, the processor utilization is  $\Theta(1)$ .

A substantial improvement over the above algorithm was given by Ajtai, Komlós & Szemerédi. They developed a parallel sorting algorithm that had no sequential counterpart. It also runs in  $O(\log n)$  time, but uses only O(n) processors, which is best possible.

### 2.2.4. Shortest paths [Dekel, Nassimi & Sahni 1981]

Given a complete directed graph with vertex set  $\{1,...,n\}$  and a length  $c_{ij}$  for each arc (i,j), one wishes to find the shortest path lengths for all pairs of vertices. Lawler [1976] gives an algorithm which requires  $O(n^3 \log n)$  time. It is based on matrix multiplication. Let  $d_{ij}^{(l)}$  denote the length of a shortest path from vertex i to vertex j, containing no more than l arcs. Since a path from vertex i to vertex j consisting of at most 2l arcs can be split into two paths of no more than l arcs each, we have that  $d_{ij}^{(2l)} = \min_{k \in \{1,...,n\}} \{d_{ik}^{(l)} + d_{kj}^{(l)}\}$ . Taking into account that a shortest path, if it exists, contains at most n-1 arcs, we obtain the following algorithm:

```

par [1 \le i, j \le n] d_{ij}^{(1)} \leftarrow c_{ij};

for m \leftarrow 1 to \lceil \log n \rceil do

l \leftarrow 2^m,

par [1 \le i, j \le n] d_{ii}^{(l)} \leftarrow \min\{d_{ik}^{(l/2)} + d_{ki}^{(l/2)} | 1 \le k \le n\}.

```

Application of the routine of Section 2.2.1 with maximization replaced by minimization yields an algorithm which requires  $O(\log^2 n)$  time and  $O(n^3/\log n)$  processors, with a processor utilization of  $\Theta(1)$ .

Greenberg, Ladner, Paterson and Galil [1982] showed that two  $n \times n$  matrices can be multiplied on a PRAM in  $O(\log n)$  time using  $O(n^{\alpha}/\log n)$  processors, with  $\alpha$  the exponent for matrix multiplication ( $\alpha \le 2.376$  [Coppersmith & Winograd 1987]). This improves the shortest paths algorithm to  $O(\log^2 n)$  time and  $O(n^{\alpha}/\log n)$  processors, with a processor utilization of  $\Theta(1)$ .

2.2.5. Minimum spanning tree [Savage & Ja'Ja' 1981; Chin, Lam & Chen 1982] The Prim-Dijkstra algorithm for the minimum spanning tree problem was discussed in Section 1.4.4. A minimum spanning tree of a complete undirected graph G with vertex set  $\{1,...,n\}$  and a length  $c_{ij}$  for each edge  $\{i,j\}$  can also be found in  $O(n^2)$  time by an algorithm due to Sollin [Berge & Ghouila-Houri 1962]. We assume that the edge lengths are all distinct; if not, we number the edges in some arbitrary way and say that from two edges with the same length the one with the lowest number is smaller. The algorithm starts with n components, each consisting of a different vertex, and with an empty set of edges belonging to the tree. At each step of the algorithm, each component finds an edge of minimum length between any of its own vertices and a vertex of a different component. Since all edge lengths are different, the edges thus obtained do not form cycles between the components and are added to the minimum spanning tree. We now merge the components which are connected by the newly found edges into a new one, and perform a next step of the algorithm as long as there is more than one component left. Because the number of components is at least halved at each step, the algorithm terminates after at most  $\lceil \log n \rceil$  steps.

In the algorithm below, for each component a representative is chosen. Two vertices belong to the same component if they have the same representative. Let  $r_i$  (i = 1,...,n) denote the representative of the component to which vertex i belongs.

```

par [1 \le i \le n] \ r_i \leftarrow i;

for l \leftarrow 1 to \lceil \log n \rceil do

par [1 \le i \le n]

find k such that r_k \ne r_i & c_{ik} = \min\{c_{ij} \mid r_j \ne r_i, 1 \le j \le n\},

if k does not exist then a minimum spanning tree has been found

& the algorithm is stopped,

t_i \leftarrow k;

par [1 \le i \le n]

find k such that r_k = r_i & c_{kt_k} = \min\{c_{jt_j} \mid r_j = r_i, 1 \le j \le n\},

s_i \leftarrow k & t_i \leftarrow t_k;

par [1 \le i \le n] \ s_i \leftarrow \text{ if } t_{t_i} = s_i \ \& \ r_i < r_{t_i} \text{ then } 0 \text{ else } s_i;

par [1 \le i \le n] \ \text{if } r_i = i \ \& s_i \ne 0 \text{ then } \text{add edge } \{s_i, t_i\} \text{ to the tree};

par [1 \le i \le n] \ r_i \leftarrow \text{ if } s_i = 0 \text{ then } r_i \text{ else } r_{t_i};

for l^* \leftarrow 1 to \lceil \log n \rceil do par [1 \le i \le n] \ r_i \leftarrow r_r.

```

Each step of the algorithm does the following. First, each component finds the edge of minimum length between any vertex of itself and one of a different component. Of the edges found twice at the same step, one copy is eliminated. The remaining edges are added to the tree. Finally, components are merged by finding a common representative, using a recursive doubling technique which will be explained later in an algorithm for scheduling fixed jobs on identical machines.

One step of the algorithm can be performed in  $O(\log n)$  time on  $O(n^2/\log n)$  processors by application of the procedure of Section 2.2.1 with maximization replaced by minimization. The complete algorithm requires  $O(\log^2 n)$  time on  $O(n^2/\log n)$  processors, with a processor utilization of  $O(1/\log n)$ .

By a careful analysis of the above algorithm, Chin, Lam & Chen proved that it can be implemented such that it runs in  $O(\log^2 n)$  time on  $O(n^2/\log^2 n)$  processors, with a processor utilization of  $\Theta(1)$ . Savage [1977] proved that the edges of a tree can be directed towards a given vertex within the same time and processor bounds.

# 2.2.6. Maximum cardinality matching [Karp, Upfal & Wigderson 1986; Mulmuley, Vazirani & Vazirani 1987]

Given an undirected graph with vertex set V and edge set E, one wishes to find a matching of maximum cardinality. A matching is a set of vertex disjoint edges. It is perfect if each vertex is incident to an edge.

Lovász [1979] gave a randomized algorithm for deciding whether a graph has a perfect matching. It is based on the following theorem of Tutte: a graph on n vertices has a perfect matching if and only if the determinant of the  $n \times n$  matrix  $B = (b_{ij})$ , with  $b_{ij} = x_{ij}$  if  $\{i,j\} \in E$  and i < j,  $b_{ij} = -x_{ij}$  if  $\{i,j\} \in E$  and i > j, and  $b_{ij} = 0$  otherwise, is not identically zero in the variables  $x_{ij}$ . Now, we choose a random number N, substitute for each variable  $x_{ij}$  a random number from  $\{1,...,N\}$  and compute the determinant. If the determinant of B is identically zero, then we find the value zero. Otherwise, the probability that we get zero is very small. Csanky [1976] showed that computing a determinant

belongs to  $\mathcal{NC}$ . Therefore, the problem of deciding whether a graph has a perfect matching belongs to  $\mathcal{NNC}$ .

The randomized algorithms of Karp, Upfal & Wigderson and Mulmuley, Vazirani & Vazirani which actually construct a perfect matching in polylogarithmic time, if it exists, are also based on Tutte's theorem. We refer to their papers for details. As a result, the problems of constructing a maximum cardinality matching and of constructing a matching of maximum weight in a graph whose edge weights are given in unary notation also belong to  $\mathfrak{RCC}$ ; in particular, the last problem can be solved, with high probability, in  $O(\log^2 n)$  time on  $n^{3+\alpha}d_{\max}$  processors, where  $d_{\max}$  is the maximum edge weight and  $\alpha$  is the exponent for matrix multiplication (see also Section 2.2.4). The complexity of the maximum cardinality matching problem with respect to deterministic parallel computations is an open question, even for bipartite graphs.

- 2.2.7. Heuristics for the traveling salesman: double minimum spanning tree, Christofides, and nearest addition [Kindervater, Lenstra & Shmoys 1989] In the traveling salesman problem (TSP), one is given a complete undirected graph G with vertex set  $\{1,...,n\}$  and a length  $d_{ij}$  for each edge  $\{i,j\}$ , and one wishes to find a Hamiltonian cycle (i.e., a cycle passing through each vertex exactly once) of minimum total length. This is a well-known  $\mathfrak{M}$ -hard problem, and rather than trying to solve it to optimality one might decide to find an approximate solution in polynomial time. We will consider three such algo-

- (1) Double minimum spanning tree

rithms in this section.

- (i) Construct a minimum spanning tree and double its edges.

- (ii) Construct an Eulerian cycle in the graph obtained in step (i) (i.e., a cycle passing through each of its edges exactly once).

- (iii) Start at a given vertex and traverse the Eulerian cycle, skipping vertices visited before.

- (2) Christofides

- (i) Construct a minimum spanning tree and a minimum perfect matching on the vertices of odd degree in the tree.

- (ii) Construct an Eulerian cycle in the graph obtained in step (i).

- (iii) Start at a given vertex and traverse the Eulerian cycle, skipping vertices visited before.

- (3) Nearest addition

- (i) Start with a tour consisting of a given vertex and a self-loop.

- (ii) Find vertices j and k with k belonging to the tour and j not for which  $d_{jk}$  is minimal, and insert j directly before k. Repeat this step until all vertices are inserted.

For each of these heuristics, we have a bound on the worst-case performance on TSP instances that satisfy the triangle inequality, i.e.,  $d_{ij} \le d_{ik} + d_{kj}$  for all i,j,k. On these instances, the double minimum spanning tree and the nearest addition heuristics produce tours that are guaranteed to be at most twice as long as the optimum, and the Christofides heuristic always does no worse than one-and-a-half times the optimum. The crucial facts in proving these bounds

are that the minimum spanning tree is no longer than the shortest tour, that the minimum perfect matching on any subset of vertices is at most half the shortest tour, and that no tour is longer than the Eulerian cycle from which it is obtained; see Lawler, Lenstra, Rinnooy Kan & Shmoys [1985] for details.

# 2.2.7.1. Double minimum spanning tree

Phase (i) of the double minimum spanning tree algorithm (constructing a minimum spanning tree and doubling its edges) can be performed in  $O(\log^2 n)$  time with  $O(n^2/\log^2 n)$  processors; see Section 2.2.5. Phase (ii) (finding an Eulerian cycle) can be done within the same time and processor bounds using the techniques from Awerbuch, Israeli & Shiloach [1984]. For phase (iii), we first have to find the first occurrence of each vertex and then eliminate all duplications. Let  $v_1,...,v_i,...,v_{2n-1}$  denote the Eulerian tour obtained in the previous phase, where  $v_i$  is the *i*th vertex of the tour and  $v_{2n-1} = v_1$ . We proceed as follows.

```

\begin{aligned} & \text{par } [1 \leq i, j \leq 2n-1] \ c_{ij} \leftarrow \text{if } v_i = v_j \text{ then } 1 \text{ else } 0; \\ & \text{par } [1 \leq i \leq 2n-1] \ d_i \leftarrow \max\{0, 1 - \sup\{c_{ij} \mid 1 \leq j \leq i-1\}\}; \\ & \text{par } [1 \leq i \leq 2n-1] \ s_i \leftarrow \sup\{d_i \mid 1 \leq j \leq i\}. \end{aligned}

```

Note that  $d_i = 1$  if  $v_i$  occurs for the first time in the tour,  $d_i = 0$  otherwise, and that  $s_i$  denotes the number of different vertices in  $v_1,...,v_i$ . We obtain the tour  $t_1 - t_2 - ... - t_n - t_1$  by:

par

$$[1 \le i \le 2n-1]$$

if  $d_i = 1$  then  $t_{s_i} \leftarrow v_i$ .

Using the partial sums algorithm from Section 2.2.2, we can implement phase (iii) within the same resource bounds as the previous phases. Hence, we end up with an algorithm that runs in  $O(\log^2 n)$  time on  $O(n^2/\log^2 n)$  processors. Since the sequential algorithm takes  $O(n^2)$  time, we have a processor utilization of  $\Theta(1)$ .

# 2.2.7.2. Christofides

The Christofides heuristic also consists of three phases. The second and third phases are identical to the corresponding phases of the double minimum spanning tree heuristic given above. Therefore, we need focus on implementing the first phase.

It is an open question if the minimum perfect matching problem belongs to  $\mathfrak{NC}$ , but it can be solved in randomized polylog time (see Section 2.2.6). We will give a randomized approximation scheme for the Christofides heuristic, i.e., a family of algorithms that asymptotically approach its performance. More precisely, for each  $\epsilon > 0$  we give an algorithm that runs in polylogarithmic time on a polynomial number of processors and, if the distances satisfy the triangle inequality, has probability of greater than .5 of delivering a tour of length less than  $3/2 + \epsilon$  times the shortest tour length; the running time is independent of  $\epsilon$  and the number of processors is polynomial in  $1/\epsilon$ . The approach is based on the idea that an approximate minimum perfect matching will suffice to obtain an approximate Christofides tour and that an approximate minimum perfect

matching can be obtained by solving a matching problem with weights bounded by a polynomial in n. It will be useful to let  $d(G) = \sum_{\{i,j\} \in E} d_{ij}$  for any graph G = (V, E) and weight function d.

For the first phase of the heuristic we construct two Eulerian graphs and select the one of smallest total length. The first of these graphs is a double minimum spanning tree. For the second we proceed as follows.

- (i) Find a minimum spanning tree T and identify the set V of vertices of odd degree in T.

- (ii) Set  $\mu = 2\epsilon d(T)/|V|$  and  $E = \{\{i,j\}\subseteq V \mid d_{ij} \le 2d(T)/3\}$ . For all  $\{i,j\}\in E$ , set  $\tilde{d}_{ij} = \lfloor d_{ij}/\mu \rfloor$ .

- (iii) Find a minimum perfect matching  $\tilde{M}$  on G = (V, E) with edge weights  $\tilde{d}$  and add these edges to the minimum spanning tree.

We first show that this procedure has the claimed performance guarantee. To do this we show that one of the Eulerian graphs produced has total length less than  $(3/2+\epsilon)d(C)$ , where C is a shortest tour. Let M denote a minimum perfect matching on V with edge weights  $d_{ij}$ . If  $d(T) \le 3d(M)/2$ , then the double minimum spanning tree has length at most  $2d(T) \le 3d(M) \le (3/2)d(C)$ .

Now assume that d(T)>3d(M)/2. Note that for each  $\{i,j\}\not\in E$ ,  $d_{ij}>2d(T)/3>d(M)$ , so that  $M\subseteq E$ . Since  $\mu \tilde{d}_{ij}\leqslant d_{ij}\leqslant \mu \tilde{d}_{ij}+\mu$  for  $\{i,j\}\in E$ , we have

$$d(\tilde{M}) \leq \sum_{\{i,j\} \in \tilde{M}} (\mu \tilde{d}_{ij} + \mu) = \mu \tilde{d}(\tilde{M}) + \mu |V|/2$$

$$\leq \mu \tilde{d}(M) + \epsilon d(T) \leq d(M) + \epsilon d(T) \leq (1/2 + \epsilon)d(C),$$

and hence  $d(T)+d(\tilde{M})<(3/2+\epsilon)d(C)$ .

As to the resource bounds,  $O(\log^2 n)$  time and  $(n^2 \log^2(1/\epsilon))/\log^2 n$  processors suffice for all of the computations except for finding the minimum perfect matching. This subroutine requires  $O(\log^2 n)$  time and  $n^{3+\alpha}\tilde{d}_{\max}$  processors, with  $\tilde{d}_{\max}$  the maximum over all values  $\tilde{d}_{ij}$  and  $\alpha$  the exponent for matrix multiplication (cf. Section 2.2.6). By observing that

tiplication (cf. Section 2.2.6). By observing that

$$\max_{\{i,j\} \in V} \tilde{d}_{ij} \leq \lfloor \frac{2d(T)/3}{2\epsilon d(T)/|V|} \rfloor = \lfloor \frac{|V|}{3\epsilon} \rfloor = O(n/\epsilon),$$

we conclude that the number of processors required is  $O(n^{4+\alpha}/\epsilon)$ .

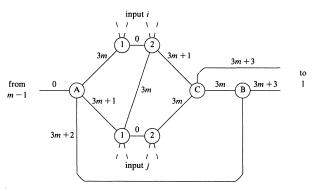

### 2.2.7.3. Nearest addition

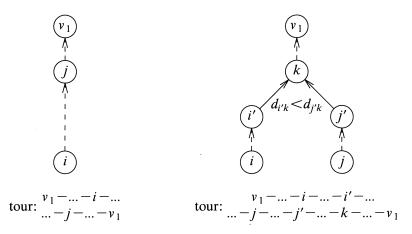

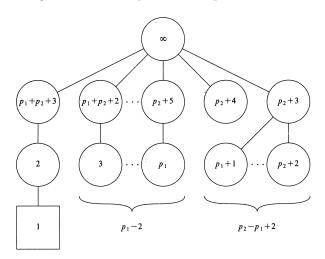

Let  $v_1$  be the given starting vertex. The order in which the nearest addition heuristic adds vertices to the tour corresponds to the way in which the algorithm from Prim and Dijkstra builds up a minimum spanning tree, starting from  $v_1$ ; see Section 1.4.4. Therefore, we first construct a minimum spanning tree and direct its edges towards  $v_1$ . By means of this tree, we can determine for each two vertices i and j which one will be visited first. There are two possible situations (Figure 2.3). In the first situation, one vertex is a descendant of the other. Since each vertex is inserted immediately before its parent, the descendant will appear earlier in the tour than the ancestor. In the second situation, no vertex is a descendant of the other. Let k be the first common ancestor of i and j and let i' (j') be the last vertex on the path from i (j) to k; i' = i

FIGURE 2.3. Nearest addition: the two possible situations for vertices i and j.

(j'=j) if the path consists of only one arc. If  $d_{i'k} < d_{j'k}$ , then vertex i' will be inserted before vertex k, and after that vertex j' will be inserted in the tour immediately before vertex k and thus after vertex i'.

A detailed description of the algorithm is given below. It has a running time of  $O(\log^2 n)$  on  $O(n^2/\log^2 n)$  processors. Without loss of generality we assume that all distances are distinct.

- (i) First, we construct a minimum spanning tree and direct it towards vertex  $v_1$ , generating arcs (i,t(i)) for  $i \in \{1,...,n\} \setminus v_1$ . For convenience, we assume  $t(v_1) = v_1$ . This requires  $O(\log^2 n)$  time and  $O(n^2/\log^2 n)$  processors (cf. Section 2.2.5).

- (ii) The next step is to construct an  $n \times n$  0-1 matrix  $(c_{ij})$ , representing the transitive closure of the tree  $(c_{ij} = 1 \text{ if there exist a path from vertex } i \text{ to vertex } j, c_{ij} = 0 \text{ otherwise})$ . Let u(i,l) denote the vertex at distance  $2^l$  from vertex i, or  $v_1$  if this vertex does not exist. The following statements do the job:

```

\begin{aligned} & \text{par} \ [1 \leqslant i \leqslant n] \ u(i,0) \leftarrow t(i); \\ & \text{for} \ l \leftarrow 1 \ \text{to} \ \lceil \log n \rceil \ \text{do} \\ & \text{par} \ [1 \leqslant i \leqslant n] \ u(i,l) \leftarrow u(u(i,l-1),l-1); \\ & \text{par} \ [1 \leqslant i,j \leqslant n] \ \text{if} \ i = j \ \text{then} \ c_{ij} \leftarrow 1 \ \text{else} \ c_{ij} \leftarrow 0 \\ & \text{for} \ l \leftarrow \lceil \log n \rceil \ \text{downto} \ 0 \ \text{do} \\ & \text{par} \ [1 \leqslant i,j \leqslant n] \ \text{if} \ c_{ij} = 1 \ \text{then} \ \text{if} \ c_{iu(j,l)} = 0 \ \text{then} \ c_{iu(j,l)} \leftarrow 1. \end{aligned}

```

(The 'if  $c_{iu(j,l)} = 0$ ' condition is added to avoid simultaneous writes into  $c_{iv_1}$ .) These operations can be performed in logarithmic time with  $O(n^2)$  processors. To reduce the number of processors, we have to observe that in each iteration of the last for l loop we only have to look at those pairs (i,j) for which  $c_{ij} = 1$ . The number of these pairs doubles in each iteration. Therefore, we perform the last iterations of the for loop in a different way. We replace the computation of the c-matrix by the following, where the parameter x will be chosen later:

By choosing  $x = \lceil \log^2 n \rceil$ , we achieve a running time of  $O(\log^2 n)$  with only  $O(n^2/\log^2 n)$  processors.

(iii) Now, we compute the total number  $s_i$  of vertices in the subtree rooted by i:

```

\mathbf{par} \ [1 \leq i \leq n] \ s_i \leftarrow \mathbf{sum} \{c_{ii} \mid 1 \leq j \leq n\}.

```

Let  $r_i$  denote the number of descendants of the parent of vertex i which will be visited after vertex i in the tour:

$$\mathbf{par} \ [1 \le i \le n] \ r_i \leftarrow \mathbf{sum} \{ s_i \mid t(i) = t(j), d_{it(i)} < d_{jt(j)}, 1 \le j \le n \}; \ r_{v_i} \leftarrow 0.$$

Finally, we compute for each vertex i the total number  $q_i$  of vertices in the path  $i,...,v_1$ :

$$\mathbf{par} \left[1 \leq i \leq n\right] q_i \leftarrow \mathbf{sum} \left\{c_{ij}(1+r_i) \mid 1 \leq j \leq n\right\}$$

(if  $c_{ij} = 1$ , then 1 for j and  $r_j$  for the descendants of the parent of j), and a nearest addition traveling salesman tour has been determined. These last steps require the same time and processor bounds as the previous ones.

2.2.8. Local optimality of time-constrained traveling salesman tours [Kindervater, Lenstra & Savelsbergh 1990]

Given a traveling salesman tour (cf. Section 2.2.7), one wishes to decide whether it is k-optimal, i.e., whether it is impossible to obtain a shorter tour by the replacement of a set of k edges by another set of k edges. In the following, let the vertex set be  $\{1,...,n\}$ , let  $d_{ij}$  be the length of edge  $\{i,j\}$  (i,j=1,...,n), and let  $(v_1,...,v_n,v_{n+1})$  denote a TSP tour, where  $v_{n+1}=v_1$ . We consider the case k=2 in detail; for k>2, the same approach can be followed.

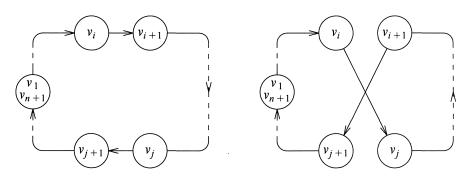

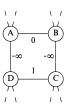

A 2-exchange replaces the edges  $\{v_i, v_{i+1}\}$  and  $\{v_j, v_{j+1}\}$  of the tour  $(v_1, ..., v_i, ..., v_j, ..., v_n, v_{n+1})$  by the edges  $\{v_i, v_j\}$  and  $\{v_{i+1}, v_{j+1}\}$ , thereby reversing the path from  $v_{i+1}$  to  $v_j$ ; see Figure 2.4. Hence, a tour is 2-optimal if it can not be improved by 2-exchanges. It is an open problem if there exists a polynomial-time algorithm that obtains 2-optimality by a sequence of 2-exchanges [Johnson, Papadimitriou & Yannakakis 1988]. We therefore restrict ourselves to deciding whether a tour is 2-optimal.

Consider the following procedure. It verifies whether or not the given tour

FIGURE 2.4. A 2-exchange.

$(v_1,...,v_n,v_{n+1})$  is 2-optimal. If not, a 2-exchange that produces a shorter tour is determined.

```

\begin{aligned} & \text{par } [1 \leq i < j \leq n] \ \delta_{ij} \leftarrow d_{\nu_i \nu_j} + d_{\nu_{i+1} \nu_{j+1}} - d_{\nu_i \nu_{i+1}} - d_{\nu_j \nu_{j+1}}; \\ & \delta_{\min} \leftarrow \min \{ \delta_{ij} \mid 1 \leq i < j \leq n \}; \\ & \text{if } \delta_{\min} \geq 0 \\ & \text{then } (\nu_1, ..., \nu_n, \nu_{n+1}) \text{ is a 2-optimal tour} \\ & \text{else let } i^* \text{ and } j^* \text{ be such that } \delta_{i^*j^*} = \delta_{\min}, \\ & (\nu_1, ..., \nu_{i^*}, \nu_{j^*}, \nu_{j^*-1}, ..., \nu_{i^*+1}, \nu_{j^*+1}, ..., \nu_{n+1}) \text{ is a shorter tour.} \end{aligned}

```

By adapting the maximum finding algorithm from Section 2.2.1 such that it computes the minimum of a set of numbers and also delivers an index for which the minimum is attained, the above procedure can be implemented to require  $O(\log n)$  time and  $O(n^2/\log n)$  processors, with a processor utilization of  $\Theta(1)$ .

Let from now on the length of edge  $\{i,j\}$  be the *travel time* between vertex i and vertex j. Assume that, as an extra condition, each vertex is given a *time window* in which it must be visited by the salesman on his tour. Arriving at a vertex before the opening of its time window introduces a waiting time at that vertex, but arriving at a vertex after the closing of its time window means infeasibility of the tour. A 2-exchange influences the arrival times at all vertices visited after the first change in the route. This may lead to infeasibility or a change in the waiting time.

The presence of time windows complexifies the problem. First, the problem of finding a feasible tour is  $\mathfrak{NP}$ -complete. Secondly, processing a single 2-exchange requires O(n) time, in contrast to O(1) time in the unconstrained case. However, Savelsbergh [1988] showed that 2-optimality can still be verified in  $O(n^2)$  time. We will give a parallel algorithm of verifying 2-optimality requiring  $O(\log n)$  time and  $O(n^2/\log n)$  processors, i.e., with the same resource requirements as in the unconstrained case.

Let  $[s_i,t_i]$  denote the time window of vertex  $v_i$  (i=1,...,n), and let a feasible tour  $(v_1,...,v_n,v_{n+1})$  be given. We start by considering paths along the given tour. With the use of these paths, we construct the tours that can be obtained

from the given tour by a 2-exchange. Our algorithm has five phases.

(i) Compute all partial sums of travel times along the tour:

```

par [1 \le i \le j \le n+1] c_{ij} \leftarrow sum\{d_{\nu_k,\nu_{k+1}} | i \le k < j\}.

```

By application of the partial sums algorithm from Section 2.2.2, this phase requires  $O(\log n)$  time and  $O(n^2/\log n)$  processors.

(ii) We now investigate the effect of the time windows on the paths along the tour. For each pair of vertices  $v_i$  and  $v_j$  with  $v_i$  before  $v_j$  on the given tour, we define  $e_{ij}$  as the earliest possible departure time at  $v_j$  when traveling along the tour from  $v_i$  to  $v_j$ , and  $e_{ji}$  as the earliest possible departure time at  $v_i$  when traveling from  $v_j$  to  $v_i$  in the reverse direction along the tour. Note that  $e_{1,n+1}$  is the arrival time at  $v_1$  of the given tour. Further, let  $l_{ij}$  denote the latest possible departure time at  $v_i$  such that the path from  $v_i$  to  $v_j$  remains feasible, and let  $l_{ji}$  denote the latest possible departure time at  $v_j$  such that the path from  $v_j$  to  $v_i$  remains feasible.

```

\begin{aligned} & \text{par } [1 \leqslant i \leqslant j \leqslant n+1] \ e_{ij} \leftarrow \max \{s_{\nu_k} + c_{kj} \ | \ i \leqslant k \leqslant j \}; \\ & \text{par } [1 \leqslant i \leqslant j \leqslant n+1] \ e_{ji} \leftarrow \max \{s_{\nu_k} + c_{ik} \ | \ i \leqslant k \leqslant j \}; \\ & \text{par } [1 \leqslant i \leqslant j \leqslant n+1] \ l_{ij} \leftarrow \min \{t_{\nu_k} - c_{ik} \ | \ i \leqslant k \leqslant j \}; \\ & \text{par } [1 \leqslant i \leqslant j \leqslant n+1] \ l_{ji} \leftarrow \min \{t_{\nu_k} - c_{kj} \ | \ i \leqslant k \leqslant j \}. \end{aligned}

```

Using the partial sums algorithm from Section 2.2.2 with addition replaced by maximization or minimization, we have the same time and processor requirements as in phase (i).

(iii) Given the earliest and latest possible departure times relative to paths along the given tour, we can compute the earliest departure time  $dep_{ij}(k)$  at any vertex  $v_k$  and the earliest arrival time  $arr_{ij}$  at the origin after the substitution of the edges  $\{v_i, v_{i+1}\}$  and  $\{v_j, v_{j+1}\}$  by the edges  $\{v_i, v_j\}$  and  $\{v_{i+1}, v_{j+1}\}$ .

```

\begin{aligned} & \text{par } [1 \leqslant i < j \leqslant n] \ dep_{ij}(j) \leftarrow \max\{e_{1i} + d_{\nu_i \nu_j}, s_{\nu_j}\}; \\ & \text{par } [1 \leqslant i < j \leqslant n] \ dep_{ij}(i+1) \leftarrow \max\{dep_{ij}(j) + c_{i+1,j}, e_{j,i+1}\}; \\ & \text{par } [1 \leqslant i < j \leqslant n] \ dep_{ij}(j+1) \leftarrow \max\{dep_{ij}(i+1) + d_{\nu_{i+1},\nu_{j+1}}, s_{\nu_{j+1}}\}; \\ & \text{par } [1 \leqslant i < j \leqslant n] \ arr_{ij} \leftarrow \max\{dep_{ij}(j+1) + c_{j+1,n+1}, e_{j+1,n+1}\}. \end{aligned}

```

For this phase, we need O(1) time using  $O(n^2)$  processors, or  $O(\log n)$  time using  $O(n^2/\log n)$  processors.

(iv) Under the assumption that the given tour  $(v_1,...,v_n,v_{n+1})$  is feasible, we can check feasibility of the tours obtained by 2-exchanges by:

```

par [1 \le i < j \le n] feas_{ij} \leftarrow (dep_{ij}(j) \le l_{i,i+1}) & (dep_{ij}(j+1) \le l_{i+1,n+1}).

```

The first condition checks feasibility at the vertices  $v_{i+1},...,v_j$  and the second one at the vertices  $v_{j+1},...,v_{n+1}$ . As in the previous phase, we need O(1) time using  $O(n^2)$  processors, or  $O(\log n)$  time using  $O(n^2/\log n)$  processors.

( $\nu$ ) Finally, we can determine 2-optimality of the given tour in the same way as in the case without time windows.

```

arr_{\min} \leftarrow \min\{arr_{ij} \mid feas_{ij}, 1 \le i < j \le n\}; if e_{1,n+1} \le arr_{\min} then (v_1,...,v_n,v_{n+1}) is a 2-optimal tour else let i^* and j^* be such that feas_{i^*j^*} & arr_{i^*j^*} = arr_{\min}, (v_1,...,v_{i^*},v_{j^*},v_{j^*-1},...,v_{i^*+1},v_{j^*+1},...,v_{n+1}) is a better feasible tour.

```

For this last part of the algorithm, the same time and processor bounds as before suffice. So, we end up with an algorithm that runs in  $O(\log n)$  time using  $O(n^2/\log n)$  processors, which is the same as in the case without time windows.

For each fixed k>2, we can derive a logarithmic-time algorithm along the same lines. One has to take into account that, given k edges, several k-exchanges are possible. Further, the influence of a k-exchange on a tour is more complex. However, it is not hard to see that the running time remains  $O(\log n)$  using  $O(n^k/\log n)$  processors, with a total computational effort as in the serial case.

## 2.2.9. Preemptive scheduling of identical machines [Dekel & Sahni 1983b]

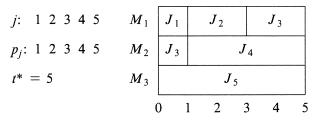

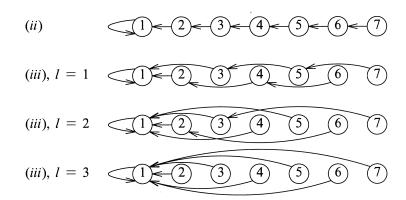

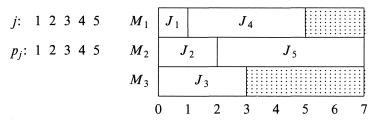

Given m identical machines  $M_i$  (i = 1,...,m) and n jobs  $J_j$ , each with a processing time  $p_j$  (j = 1,...,n), one wishes to find a preemptive schedule of minimum length. A preemptive schedule assigns to each  $J_j$  a number of triples  $(M_i,s,t)$ , where  $1 \le i \le m$  and  $0 \le s \le t$ , indicating that  $J_j$  is to be processed by  $M_i$  from time s to time t. A preemptive schedule is feasible if the processing intervals on  $M_i$  are nonoverlapping for all i, and the processing intervals of  $J_j$  are nonoverlapping and have total length  $p_j$  for all j. It is optimal if the maximum completion time of the jobs is minimum.

An optimal schedule can be found in O(n) time by the classical wrap around rule of McNaughton [1959]. The algorithm first computes a value  $t^*$  which is an obvious lower bound on the minimum schedule length. It then constructs a schedule of length  $t^*$  by considering the jobs in an arbitrary order and scheduling them in the m periods  $(0,t^*)$ , carrying over the part of a job that does not fit at the end of the period on  $M_i$  to the beginning of the period on  $M_{i+1}$ . More formally:

```

\begin{split} t^* \leftarrow \max\{\max\{p_j \mid 1 \leqslant j \leqslant n\}, \sup\{p_j \mid 1 \leqslant j \leqslant n\}/m\}; \\ s \leftarrow 0; \ i \leftarrow 1; \\ \text{for } j \leftarrow 1 \text{ to } n \text{ do} \\ \text{if } s + p_j \leqslant t^* \\ \text{then assign } (M_i, s, s + p_j) \text{ to } J_j, \\ s \leftarrow s + p_j \\ \text{else assign } (M_i, s, t^*) \text{ and } (M_{i+1}, 0, p_j - (t^* - s)) \text{ to } J_j, \\ s \leftarrow p_j - (t^* - s), \ i \leftarrow i + 1. \end{split}

```

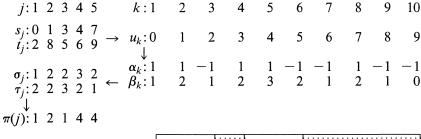

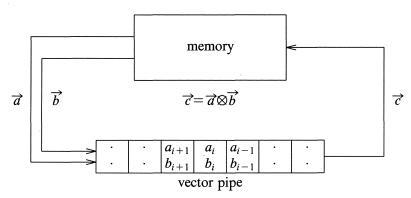

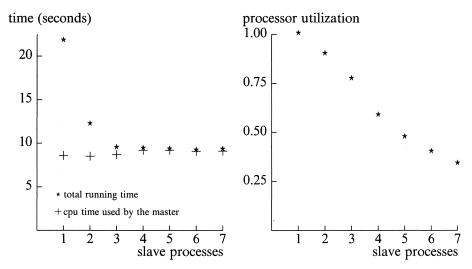

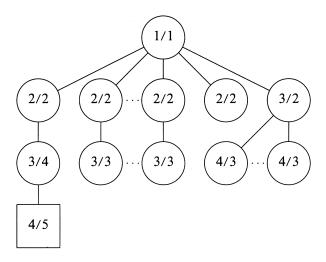

An example is given in Figure 2.5 There are two global parameters that are updated sequentially as the job index j increases: the starting time s and the machine index i of  $J_j$ . We can calculate all starting times and machine indices simultaneously in logarithmic time, using the parallel procedures for finding

FIGURE 2.5. Preemptive scheduling: an instance with m = 3 and n = 5.

the maximum and the partial sums from Sections 2.2.1 and 2.2.2 as subroutines:

```

\begin{array}{l} t^* \leftarrow \max\{\max\{p_j \mid 1 \leq j \leq n\}, \sup\{p_j \mid 1 \leq j \leq n\}/m\};\\ \mathbf{par} \ [1 \leq j \leq n] \ q_j \leftarrow \sup\{p_k \mid 1 \leq k \leq j-1\};\\ \mathbf{par} \ [1 \leq j \leq n]\\ s_j \leftarrow q_j \ \mathrm{mod} \ t^*, \ i_j \leftarrow \lfloor q_j/t^* \rfloor + 1,\\ \mathbf{if} \ s_j + p_j \leq t^*\\ \mathbf{then} \ \mathrm{assign} \ (M_{i_j}, s_j, s_j + p_j) \ \mathrm{to} \ J_j\\ \mathbf{else} \ \mathrm{assign} \ (M_{i_j}, s_j, t^*) \ \mathrm{and} \ (M_{i_j+1}, 0, p_j - (t^* - s_j)) \ \mathrm{to} \ J_j. \end{array}

```

This algorithm can be implemented to require  $O(\log n)$  time and  $O(n/\log n)$  processors with a processor utilization of  $\Theta(1)$ .

### 2.2.10. Preemptive scheduling of uniform machines [Martel 1988]

Given are m machines  $M_i$ , each with a speed  $s_i$  (i = 1,...,m), and n jobs  $J_j$ , each with a processing requirement  $p_j$  (j = 1,...,n). If  $J_j$  is completely processed on  $M_i$ , the processing time is  $p_j/s_i$  on machine  $M_i$ . One wishes to find a preemptive schedule of minimum length.

An optimal schedule can be found in  $O(n+m\log m)$  time by an algorithm due to Gonzalez & Sahni [1978]. As in the previous section, the algorithm first finds an obvious lower bound  $t^*$  on the minimum schedule length and then constructs a schedule of length  $t^*$ . Assume that the machines are ordered according to nonincreasing speeds and that the m-1 largest jobs, ordered according to nonincreasing processing requirements, precede the n-m+1 remaining jobs. The Gonzalez-Sahni algorithm is as follows:

```

t^* = \max\{(p_1/s_1), (p_1+p_2)/(s_1+s_2), ..., (p_1+...+p_{m-1})/(s_1+...+s_{m-1}), (p_1+...+p_n)/(s_1+...+s_m)\}; construct a composite machine with speed s_i in the interval [(i-1)t^*, it^*) (i=1,...,m) and speed 0 in [mt^*,\infty); for j\leftarrow 1 to n do find the latest possible interval [s,s+t^*) such that the composite machine can process J_j, assign the interval [s,s+t^*) to J_j, replace the speed of the composite machine at time s+t by the original speed of the machine at time s+t, for all t>0.

```

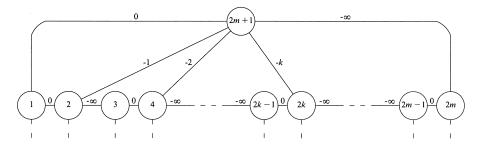

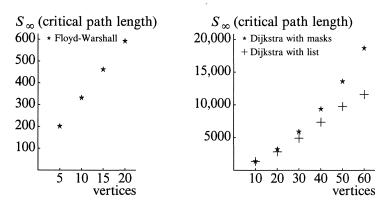

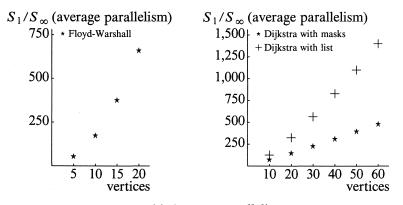

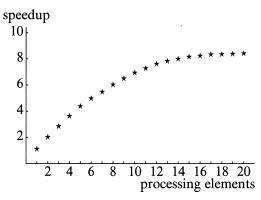

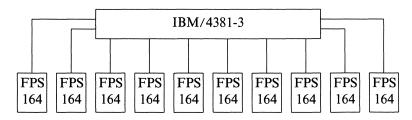

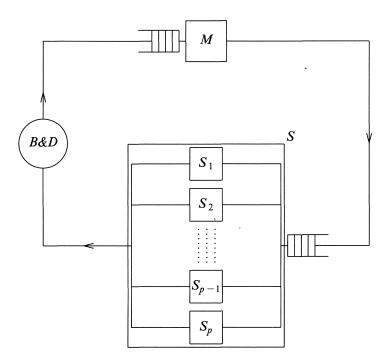

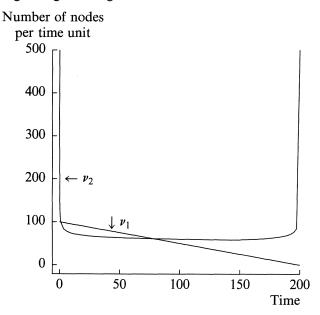

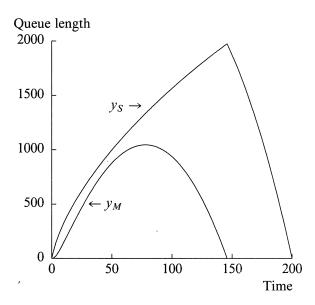

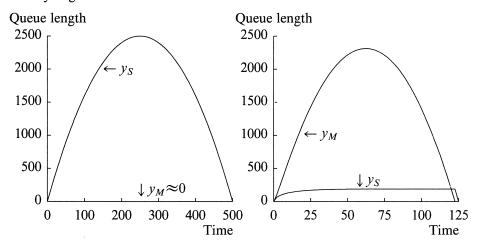

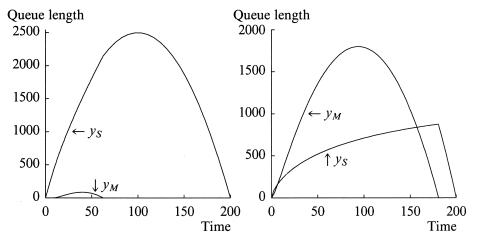

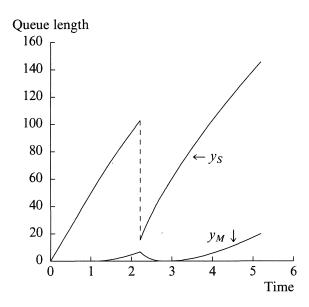

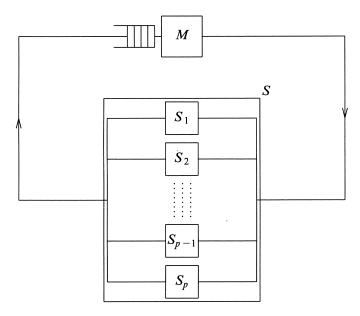

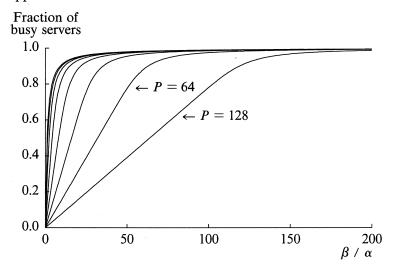

After scheduling the m-1 largest jobs, the composite machine has in any interval of length  $t^*$  with positive speed a processing capacity that is greater than the processing requirement of any of the remaining jobs. The parallel algorithm first schedules the m-1 largest jobs; after that, the remaining jobs are scheduled in the same way as in Section 2.2.9. The first phase of Martel's algorithm is only sketched here; the full story can be found in his paper.